Altera JESD204B IP User Manual

Page 145

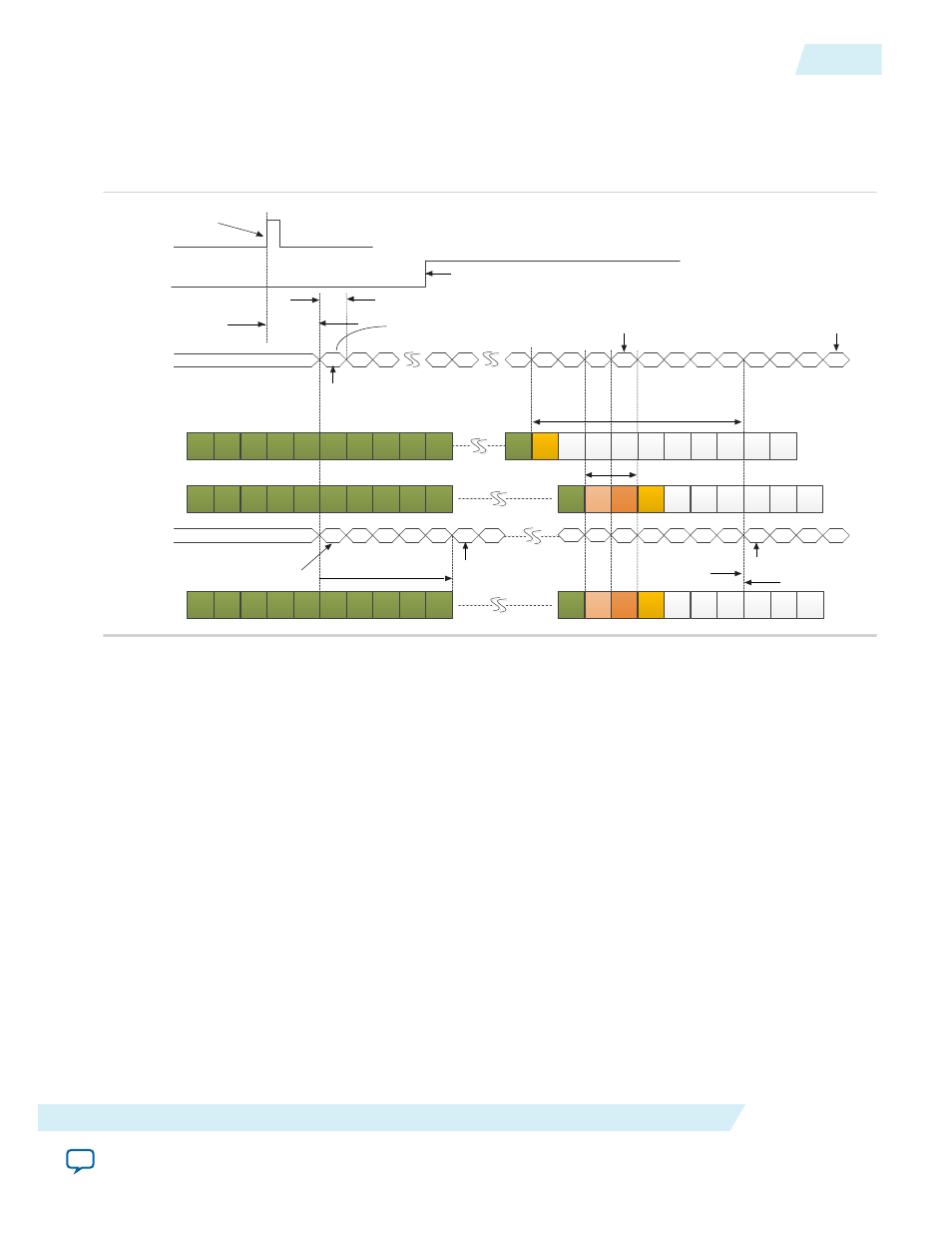

You should set a safe LMFC offset value to ensure deterministic latency from one power cycle to another

, the illegal csr_lmfc_offset values of 1, 2, and 3 will cause lane de-skew error

because the RBD buffer size has exceeded.

Figure 6-6: Selecting Illegal LMFC Offset Value for RX, Causing Lane Deskew Error

First LMFC

boundary

SYSREF pulse is

sampled by IP core ‘s

internal register

2 link clock cycle deterministic

delay from SYSREF sampled

high to the first LMFC boundary

Free running LMFC counter

Internal

LMFC Counter

0

1

2

0

1

4

0

1

2

3

4

5

6

7

K

SYNC_N deasserted at LMFC boundary

K

K

K

K

R

K

K

K

K

K

Latest arrival

lane in multiple

power cycles

D

D

D

D

0

Power cycle variation

Fourth LMFC

boundary

1 link clock period = LMFC count

Internal LMFC counter resets

csr_lmfc_offset=0

7

Third LMFC

boundary

D

D

SYNC_N

transmitted by RX

R

R

Free running LMFC counter

Internal

LMFC Counter

3

4

5

6

7

0

1

3

4

5

6

7

0

1

2

3

RBD elastic buffer

released

when csr _rbd_offset=0

2

K

K

K

K

K

K

K

K

K

K

Internal LMFC counter resets

csr_lmfc_offset=3

LMFC boundary is

delayed by 5 link clock

First LMFC boundary

at new location

R

D

D

D

D

D

D

R

R

6

1

K

K

Latest arrival

lane in multiple

power cycles

K

K

K

K

K

R

K

K

K

K

K

Earliest arrival

lane

D

D

D

D

D

D

K

5

RBD elastic buffer size = 8

D

D

D

RBD elastic buffer

size is exceeded

rx_sysref

Third LMFC boundary at new location

You can use the TX LMFC offset to align the LMFC counter in IP core to the LMFC counter in DAC.

UG-01142

2015.05.04

Programmable LMFC Offset

6-7

JESD204B IP Core Deterministic Latency Implementation Guidelines

Altera Corporation