Run-time reconfiguration – Altera JESD204B IP User Manual

Page 124

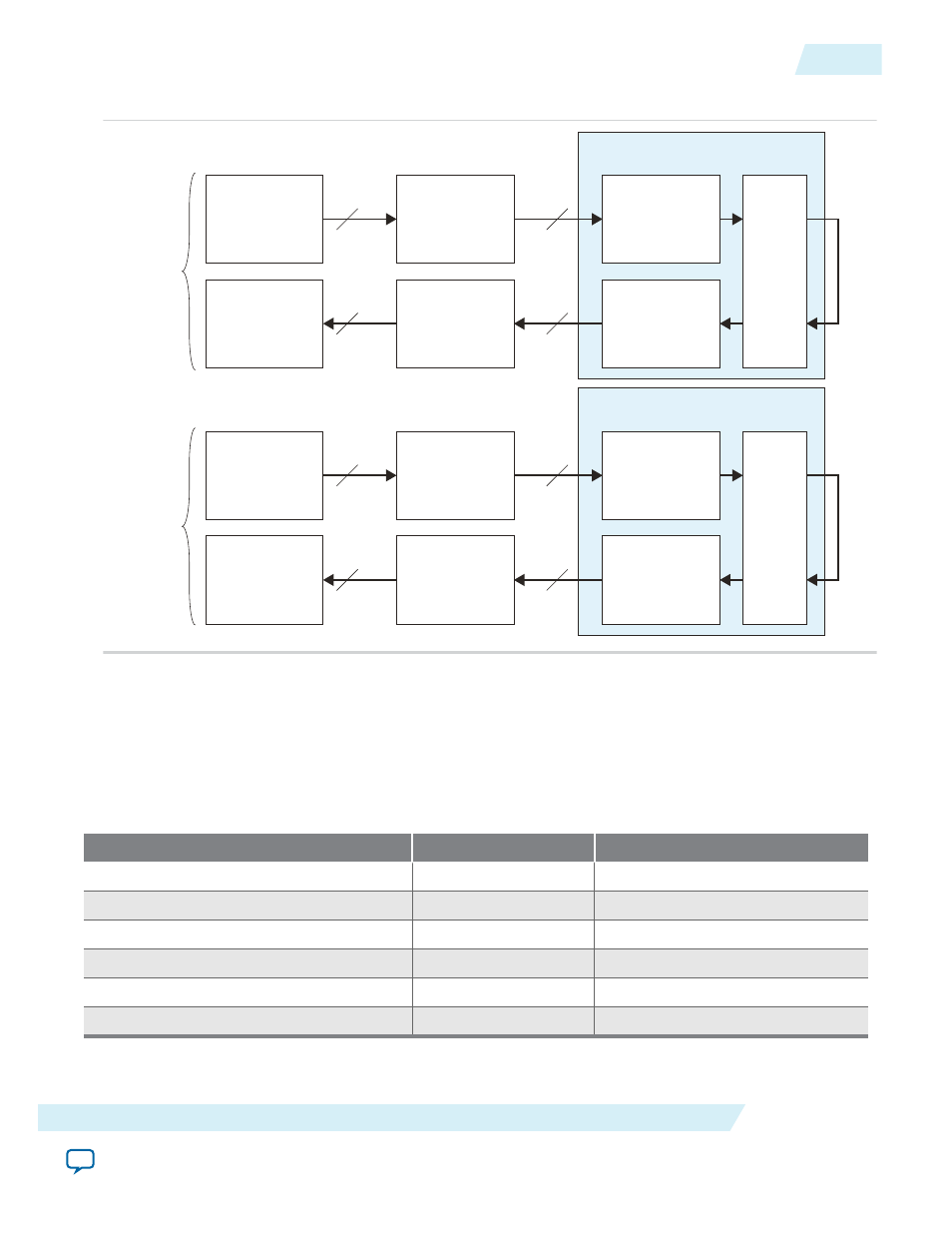

Figure 5-18: Datapath of Multiple JESD204B Links

32

32

16

16

Avalon-ST

Avalon-ST

Avalon-ST

Avalon-ST

Transport Layer 0

JESD204B IP Duplex Core 0 (LMF = 112)

Pattern Generator 0

Pattern Checker 0

Assembler

LMF = 112, S = 1,

N = 16

Deassembler

LMF = 112, S = 1,

N = 16

TX Base Core

LMF = 112, S = 1,

N = 16

RX Base Core

LMF = 112, S = 1,

N = 16

Duplex

SERDES

PHY

32

32

16

16

Avalon-ST

Avalon-ST

Avalon-ST

Avalon-ST

Transport Layer 1

Pattern Generator 1

Pattern Checker 1

Assembler

LMF = 112, S = 1,

N = 16

Deassembler

LMF = 112, S = 1,

N = 16

TX Base Core

LMF = 112, S = 1,

N = 16

RX Base Core

LMF = 112, S = 1,

N = 16

Duplex

SERDES

PHY

LINK 0

LINK 1

M = 1, S = 1, N = 16,

FRAMECLK_DIV = 1

M = 1, S = 1, N = 16,

FRAMECLK_DIV = 1

M = 1, S = 1, N = 16,

FRAMECLK_DIV = 1

M = 1, S = 1, N = 16,

FRAMECLK_DIV = 1

JESD204B IP Duplex Core 1 (LMF = 112)

Run-Time Reconfiguration

The JESD204B IP core supports run-time reconfiguration for the LMF and data rate settings. The design

example only demonstrates the following set of configuration.

To generate the design example with run-time reconfiguration enabled, the LMF and bonding mode

parameters must match the default value listed in the table below.

Table 5-20: Run-time Reconfiguration Demonstrated By The Design Example

Parameter

Default

Run-time Reconfiguration

LMF

222

112

FRAMECLK_DIV

2

2

Data Rate

6144 Mbps

3072 Mbps

Link Clock

153.6 MHz

76.8 MHz

Frame Clock

153.6 MHz

76.8 MHz

Bonding Mode

Non-bonded

Non-bonded

UG-01142

2015.05.04

Run-Time Reconfiguration

5-43

JESD204B IP Core Design Guidelines

Altera Corporation