Altera JESD204B IP User Manual

Page 127

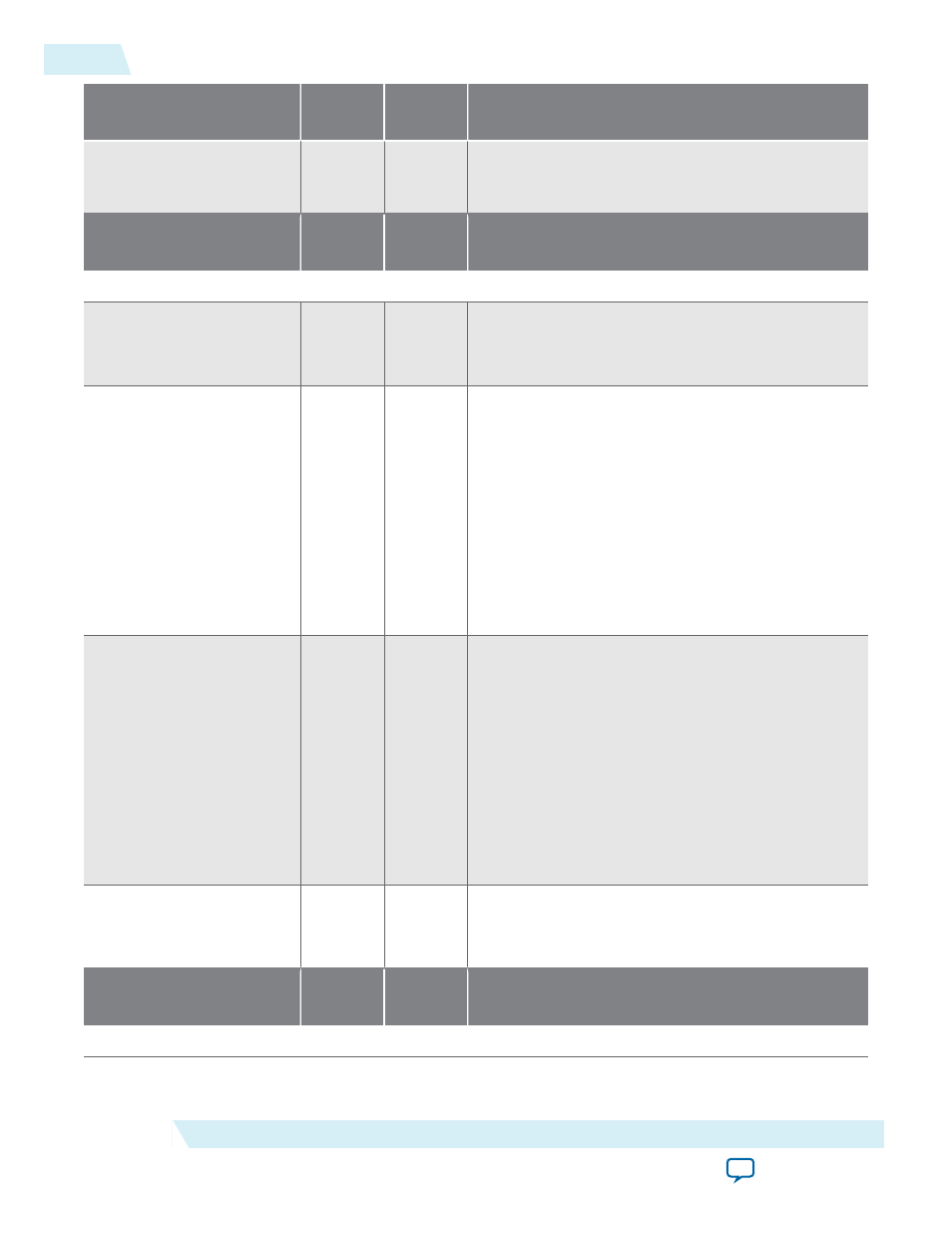

Signal

Clock

Domain

Direction

Description

rx_

seriallpbken[LINK*L-

1:0]

—

Input

Assert this signal to enable internal serial loopback in

the duplex transceiver.

Signal

Clock

Domain

Direction

Description

User Request Control

reconfig

mgmt_clk

Input

Active high reconfiguration request. Set this signal to

static 0 during compile time if run time reconfigura‐

tion is not required.

runtime_lmf

mgmt_clk

Input

Reconfigure the LMF value at run-time. This value

must be stable prior to assertion of the

reconfig

signal.

• 0—Downscale to the LMF value stored in MIF

file.

• 1— Upscale back to maximum LMF value.

Assuming at compile time, the LMF configuration is

222, set this signal to 0 to scale down the LMF

configuration to 112. Set this signal to 1 to scale up

the LMF configuration back to 222.

runtime_datarate

mgmt_clk

Input

Reconfigure the data rate at run-time. This value

must be stable prior to assertion of

reconfig

signal.

• 0— Downscale to data rate setting stored in PLL,

PHY, and clock MIF.

• 1— Upscale back to maximum data rate setting

stored in PLL, PHY, and clock MIF.

Assuming the compile time data rate is 3.072 Gbps,

set this signal to 0 to scale down the data rate to 1.536

Gbps. Set this signal to 1 to scale up the data rate

back to 3.072 Gbps.

cu_busy

mgmt_clk

Output

Assert high to indicate that the control unit is busy.

All reconfiguration input will be ignored when this

signal is high.

Signal

Clock

Domain

Direction

Description

Avalon- ST User Data

5-46

System Interface Signals

UG-01142

2015.05.04

Altera Corporation

JESD204B IP Core Design Guidelines