Altera JESD204B IP User Manual

Page 67

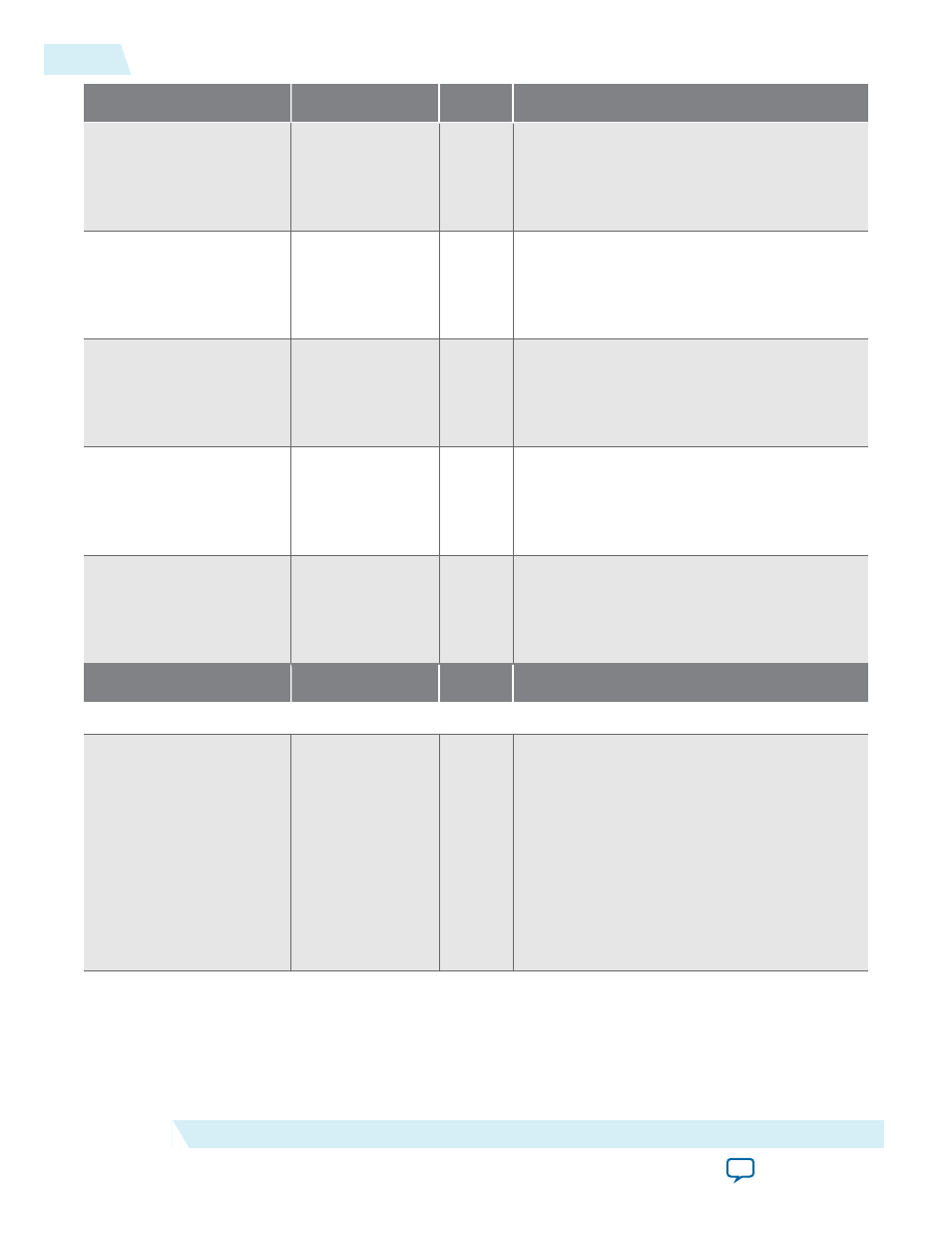

Signal

Width

Direction

Description

reconfig_avmm_

writedata[]

32

Input

The input data.

This signal is only available if you enable

dynamic reconfiguration for Arria 10 FPGA

variants.

reconfig_avmm_

readdata[]

32

Output

The output data.

This signal is only available if you enable

dynamic reconfiguration for Arria 10 FPGA

variants.

reconfig_avmm_write

1

Input

Write signal. This signal is active high.

This signal is only available if you enable

dynamic reconfiguration for Arria 10 FPGA

variants.

reconfig_avmm_read

1

Input

Read signal. This signal is active high.

This signal is only available if you enable

dynamic reconfiguration for Arria 10 FPGA

variants.

reconfig_avmm_

waitrequest

1

Output

Wait request signal.

This signal is only available if you enable

dynamic reconfiguration for Arria 10 FPGA

variants.

Signal

Width

Direction

Description

Avalon-ST Interface

jesd204_tx_link_

data[]

L*32

Input

Indicates a 32-bit user data at

txlink_clk

clock rate, where four octets are packed into a

32-bit data width per lane. The data format is

big endian.

The first octet is located at bit[31:24], followed

by bit[23:16], bit[15:8], and the last octet is

bit[7:0]. Lane 0 data is always located in the

lower 32-bit data. If more than one lane is

instantiated, lane 1 is located at bit[63:32],

with the first octet position at bit[63:56].

4-30

Transmitter

UG-01142

2015.05.04

Altera Corporation

JESD204B IP Core Functional Description