Altera JESD204B IP User Manual

Page 77

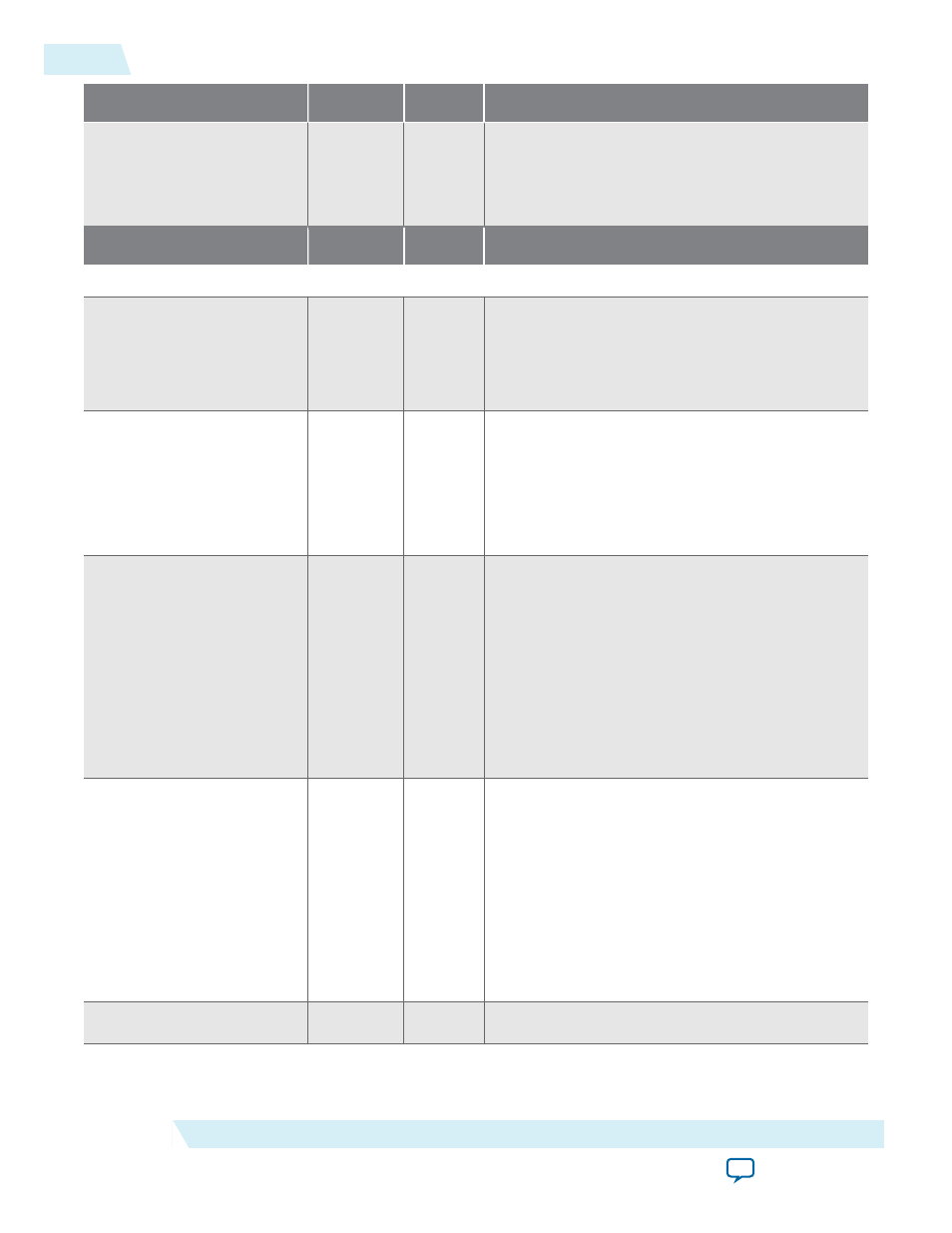

Signal

Width

Direction

Description

jesd204_rx_avs_

waitrequest

1

Output

This signal is asserted by the Avalon-MM slave to

indicate that it is unable to respond to a read or

write request. The JESD204B IP core ties this

signal to 0 to return the data in the access cycle.

Signal

Width

Direction

Description

JESD204 Interface

sysref

1

Input

SYSREF signal for JESD204B Subclass 1

implementation.

For Subclass 0 and Subclass 2 mode, tie-off this

signal to 0.

dev_sync_n

1

Output

Indicates a SYNC~ from the receiver. This is an

active low signal and is asserted 0 to indicate a

synchronization request. Instead of reporting the

link error through this signal, the JESD204B IP

core uses the

jesd204_rx_int

signal to interrupt

the CPU.

sof[]

4

Output

Indicates a start of frame.

• [3]—start of frame for

jesd204_rx_link_

data[31:24

]

• [2]—start of frame for

jesd204_rx_link_

data[23:16]

• [1]—start of frame for

jesd204_rx_link_

data[15:8]

• [0]—start of frame for

jesd204_rx_link_

data[7:0]

somf[]

4

Output

Indicates a start of multiframe.

• [3]—start of multiframe for

jesd204_rx_link_

data[31:24

]

• [2]—start of multiframe for

jesd204_rx_link_

data[23:16]

• [1]—start of multiframe for

jesd204_rx_link_

data[15:8]

• [0]—start of multiframe for

jesd204_rx_link_

data[7:0]

dev_lane_aligned

1

Output

Indicates that all lanes for this device are aligned.

4-40

Receiver

UG-01142

2015.05.04

Altera Corporation

JESD204B IP Core Functional Description