Altera JESD204B IP User Manual

Page 126

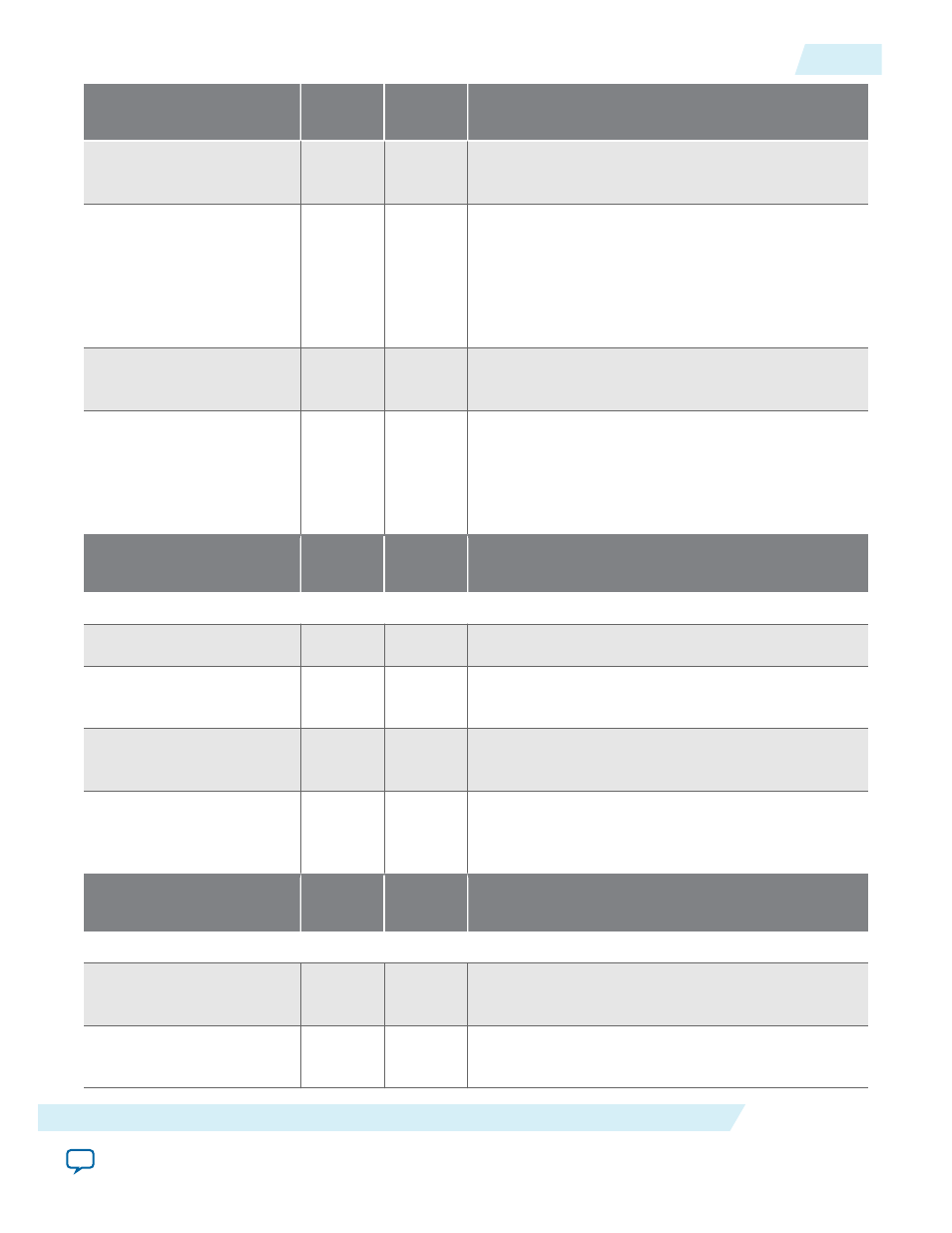

Signal

Clock

Domain

Direction

Description

rx_sysref[LINK-1:0]

link_clk

Input

RX SYSREF signal for JESD204B Subclass 1

implementation.

tx_dev_sync_n[LINK-

1:0]

link_clk

Output

Indicates a clean synchronization request at the TX

path. This is an active low signal and is asserted 0 to

indicate a synchronization request. The

SYNC_N

signal error reporting is masked out of this signal.

This signal is also asserted during software-initiated

synchronization.

dev_lane_

aligned[LINK-1:0]

link_clk

Output

Indicates that all lanes for this device are aligned at

the RX path.

rx_dev_sync_n[LINK-

1:0]

link_clk

Output

Indicates a

SYNC_N

to the transmitter. This is an

active low signal and is asserted 0 to indicate a

synchronization request. Instead of reporting the link

error through this signal, the JESD204B IP core uses

the

jesd204_rx_int

signal to indicate an interrupt.

Signal

Clock

Domain

Direction

Description

SPI

miso

sclk

Input

Output data from a slave to the input of the master.

mosi

sclk

Output

Output data from the master to the inputs of the

slaves.

sclk

mgmt_clk

Output

Clock driven by the master to slaves, to synchronize

the data bits.

ss_n[2:0]

sclk

Output

Active low select signal driven by the master to

individual slaves, to select the target slave. Defaults to

3 bits.

Signal

Clock

Domain

Direction

Description

Serial Data and Control

rx_serial_

data[LINK*L-1:0]

—

Input

Differential high speed serial input data. The clock is

recovered from the serial data stream.

tx_serial_

data[LINK*L-1:0]

device_

clk

Output

Differential high speed serial output data. The clock

is embedded in the serial data stream.

UG-01142

2015.05.04

System Interface Signals

5-45

JESD204B IP Core Design Guidelines

Altera Corporation