Altera JESD204B IP User Manual

Page 13

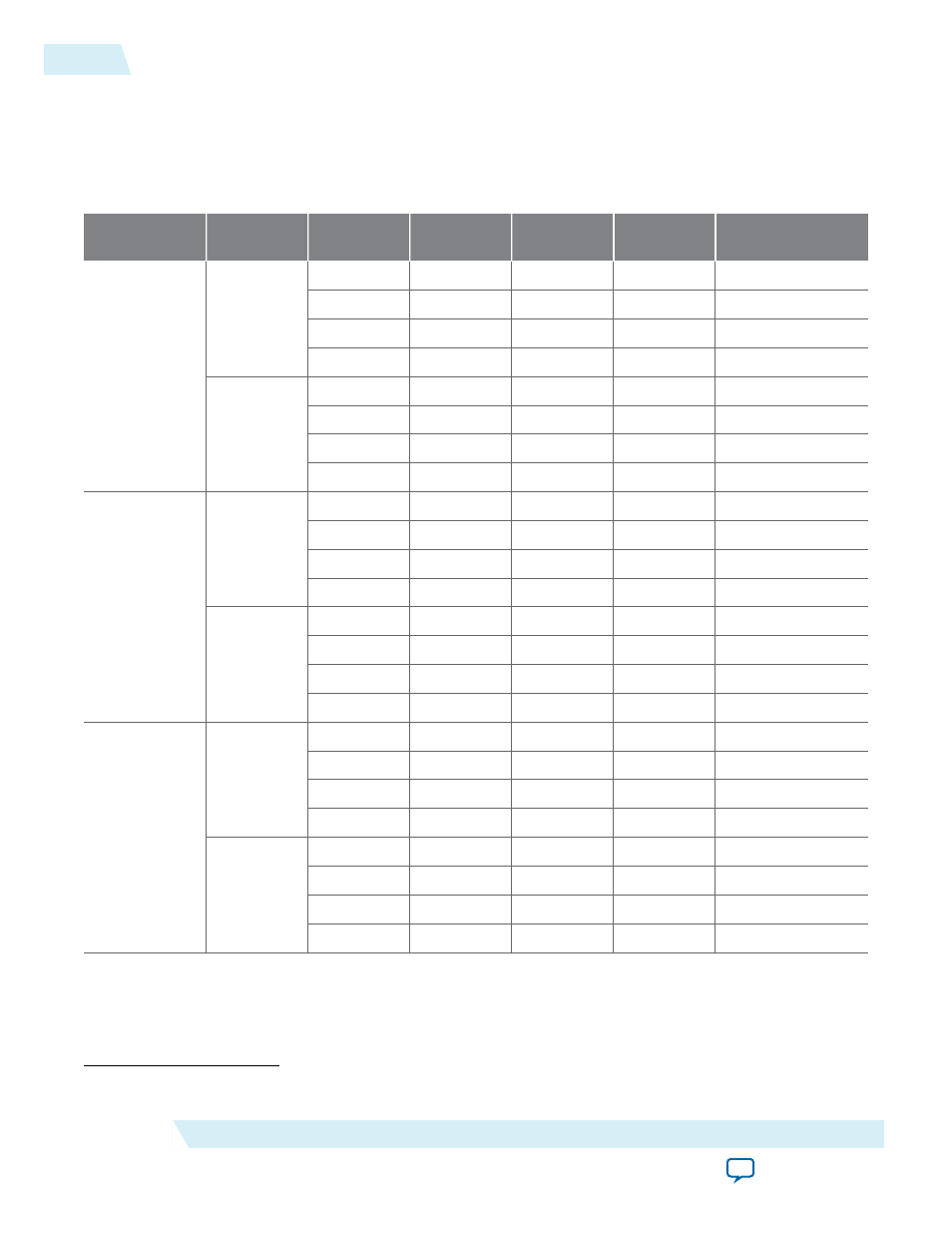

Table 2-5: JESD204B IP Core Resource Utilization

The numbers of ALMs and logic registers in this table are rounded up to the nearest 10.

Note: The resource utilization data are extracted from a full design which includes the Altera Transceiver PHY

Reset Controller IP Core. Thus, the actual resource utilization for the JESD204B IP core should be smaller

by about 15 ALMs and 20 registers.

Device Family

Data Path

Number of

Lanes

ALMs

ALUTs

Logic

Registers

Memory Block

(M10K/M20K)

(6)

(7)

Cyclone V

RX

1

1047

1543

1200

1

2

1594

2325

1825

2

4

2832

4043

3080

4

8

5354

7525

5585

8

TX

1

728

1148

948

0

2

889

1424

1066

0

4

1218

1941

1293

0

8

1715

2837

1757

0

Arria V

RX

1

1052

1543

1197

1

2

1586

2325

1823

2

4

2830

4043

3077

4

8

5330

7525

5584

8

TX

1

719

1148

947

0

2

887

1424

1062

0

4

1208

1941

1292

0

8

1724

2853

1754

0

Arria V GZ

RX

1

1062

1542

1215

0

2

1634

2363

1858

0

4

2934

4097

3141

0

8

5526

7697

5711

0

TX

1

728

1150

948

0

2

937

1488

1083

0

4

1365

2114

1354

0

8

2141

3417

1895

0

(6)

M10K for Arria V device, M20K for Arria V GZ, Stratix V and Arria 10 devices.

2-8

Performance and Resource Utilization

UG-01142

2015.05.04

Altera Corporation

About the JESD204B IP Core

- MAX 10 JTAG (15 pages)

- MAX 10 Power (21 pages)

- Unique Chip ID (12 pages)

- Remote Update IP Core (43 pages)

- Device-Specific Power Delivery Network (28 pages)

- Device-Specific Power Delivery Network (32 pages)

- Hybrid Memory Cube Controller (69 pages)

- ALTDQ_DQS IP (117 pages)

- MAX 10 Embedded Memory (71 pages)

- MAX 10 Embedded Multipliers (37 pages)

- MAX 10 Clocking and PLL (86 pages)

- MAX 10 FPGA (26 pages)

- MAX 10 FPGA (56 pages)

- USB-Blaster II (22 pages)

- GPIO (22 pages)

- LVDS SERDES (27 pages)

- User Flash Memory (33 pages)

- ALTDQ_DQS2 (100 pages)

- Avalon Tri-State Conduit Components (18 pages)

- Cyclone V Avalon-MM (166 pages)

- Cyclone III FPGA Starter Kit (36 pages)

- Cyclone V Avalon-ST (248 pages)

- Stratix V Avalon-ST (286 pages)

- Stratix V Avalon-ST (293 pages)

- DDR3 SDRAM High-Performance Controller and ALTMEMPHY IP (10 pages)

- Arria 10 Avalon-ST (275 pages)

- Avalon Verification IP Suite (224 pages)

- Avalon Verification IP Suite (178 pages)

- FFT MegaCore Function (50 pages)

- DDR2 SDRAM High-Performance Controllers and ALTMEMPHY IP (140 pages)

- Floating-Point (157 pages)

- Integer Arithmetic IP (157 pages)

- Embedded Peripherals IP (336 pages)

- Low Latency Ethernet 10G MAC (109 pages)

- LVDS SERDES Transmitter / Receiver (72 pages)

- Nios II Embedded Evaluation Kit Cyclone III Edition (3 pages)

- Nios II Embedded Evaluation Kit Cyclone III Edition (80 pages)

- IP Compiler for PCI Express (372 pages)

- Parallel Flash Loader IP (57 pages)

- Nios II C2H Compiler (138 pages)

- RAM-Based Shift Register (26 pages)

- RAM Initializer (36 pages)

- Phase-Locked Loop Reconfiguration IP Core (51 pages)

- DCFIFO (28 pages)