The ftxl hardware abstraction layer, Managing the ftxl transceiver – Echelon FTXL User Manual

Page 190

178

FTXL LonTalk API

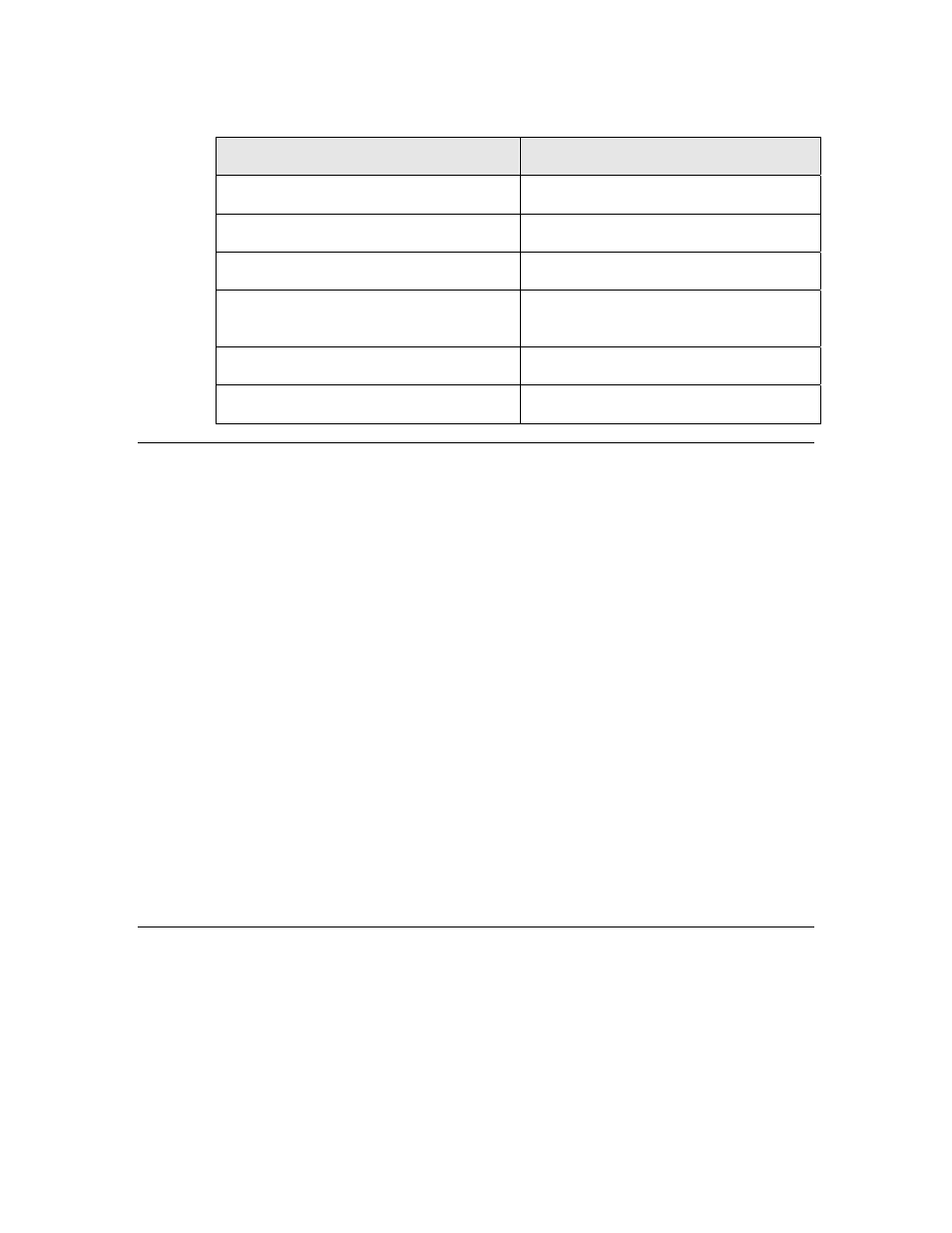

Table 43. MicroC/OS-II Timer Management Options

Option

Setting for FTXL Applications

Maximum number of timers

Not required

Determine the size of a timer name

Not required

Size of timer wheel

Not required

Rate at which timer management task

runs

Not required

Stack size for timer task

Not required

Priority of timer task

Not required

The FTXL Hardware Abstraction Layer

The FTXL Developer’s Kit includes a hardware abstraction layer (HAL) that

provides an abstract interface for the FTXL Transceiver. The FTXL HAL is

independent of the Altera HAL, which provides an abstract interface to the Nios

II processor and other hardware components for the FPGA device.

The example applications that are included with the FTXL Developer’s Kit

implement the FTXL HAL for the FTXL Transceiver Board and the DBC2C20

development board. The FTXL HAL is provided as source code so that you can

modify this implementation to support other hardware configurations. However,

if your design uses the same signal names and the same basic logic as are used in

the reference design that is included with the example applications, you can

likely use the functions in the FtxlHal.c with little or no change.

For detailed information about the FTXL HAL, see the HTML API

documentation and the API source code:

• HTML API documentation: Start → Programs → Echelon FTXL

Developer’s Kit → Documentation → API Reference

• API source code: Start → Programs → Echelon FTXL Developer’s Kit →

Source Code

The following sections provide an overview of the functions that the FTXL HAL

provides. See the

FTXL Hardware Guide

for a description of the FTXL

Transceiver hardware interface.

Managing the FTXL Transceiver

To manage the FTXL Transceiver, the FTXL HAL provides the functions listed in

Table 44 on page 179.