ADLINK PCIe-7360 User Manual

Page 76

66

Operations

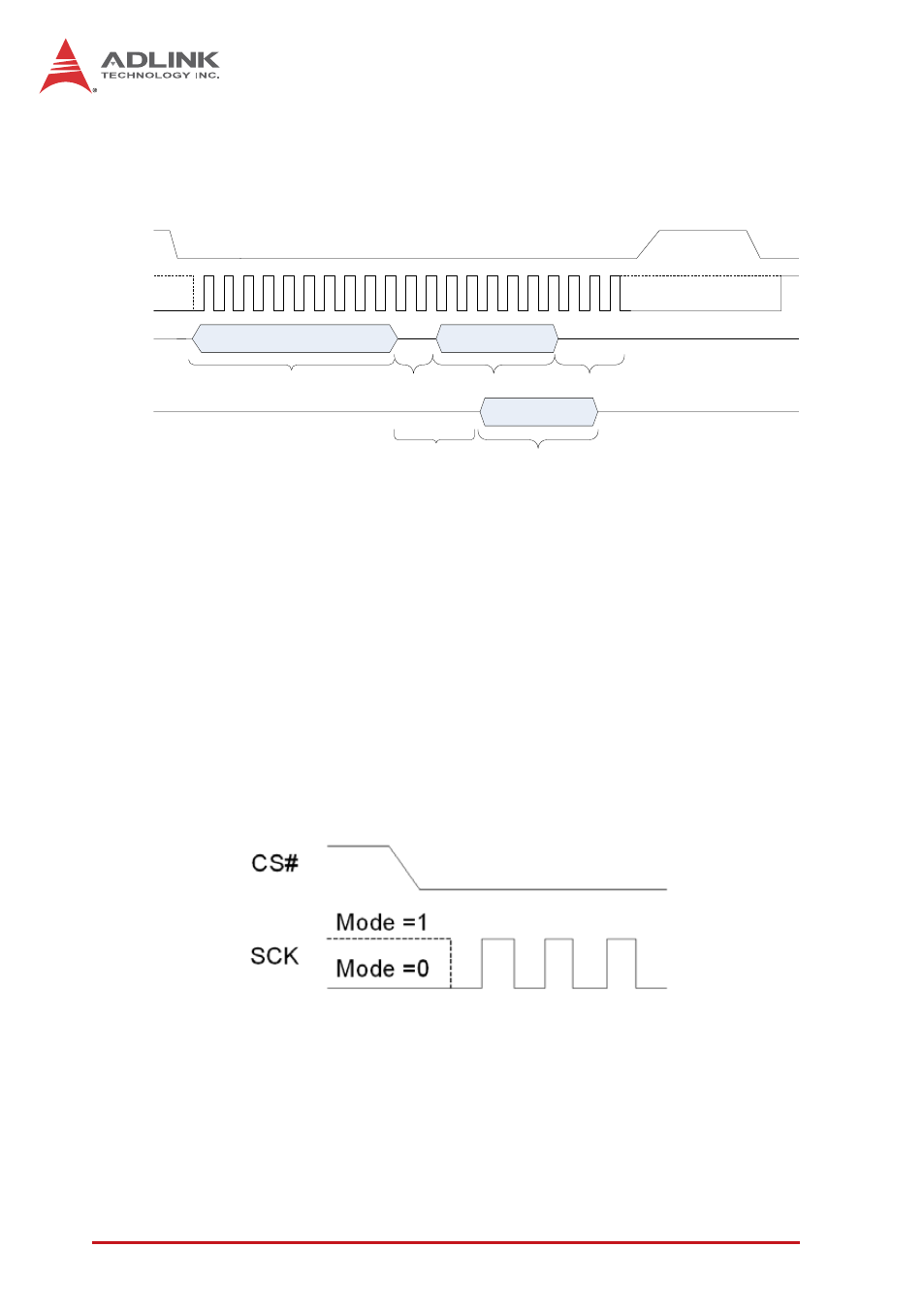

SPI master of PCIe-7360 provide at most 64 bits -- 32 bits

address/ command and 32 bits data. SPI master of PCIe-7360

supports only one slave device. Figure 3-32 shows the data trans-

fer on SPI bus.

Figure 3-33: Data Transfer on SPI Bus

SPI master of PCIe-7360 supports clock frequency range from

244.14 kHz to 62.5 MHz. After issuing command to SPI slave

device, the clock rate might be changed according the request

from SPI slave. The below formula is to calculate the SPI clock

rate.

Fscl = 62.5 / (Clk Pre-scale + 1) (MHz),

where Clk Pre-scale=0 to 255

SPI master of PCIe-7360 supports two different modes of SCK.

Clock modes 0 and 1 of SCK are as shown.

Figure 3-34: Clock Mode of SCK

CS#

SCK

Data

Data

SDO

SDI

Cmd/Addr

Cmd/Addr 0 ~ 32b

RD 0 ~ 32b

TD 0 ~ 32b

dummy

dummy

dummy

- USB-1901 (84 pages)

- USB-1210 (54 pages)

- USB-2401 (60 pages)

- USB-7230 (50 pages)

- USB-2405 (56 pages)

- DAQe-2010 (92 pages)

- DAQe-2204 (100 pages)

- DAQe-2213 (94 pages)

- DAQe-2501 (74 pages)

- PXI-2010 (84 pages)

- PXI-2020 (60 pages)

- PXI-2501 (62 pages)

- cPCI-9116 (98 pages)

- ACL-8112 Series (94 pages)

- ACL-8112 Series (92 pages)

- ACL-8112 Series (93 pages)

- ACL-8216 (75 pages)

- ACL-8111 (61 pages)

- PCM-9112+ (10 pages)

- PCM-9112+ (94 pages)

- cPCI-6216V (47 pages)

- ACL-6126 (28 pages)

- ACL-6128A (40 pages)

- PCM-6308V+ (52 pages)

- PCM-6308V+ (4 pages)

- PCI-7444 (82 pages)

- PCI-7434 (48 pages)

- PCI-7234 (56 pages)

- PCI-7260 (66 pages)

- PCI-7258 (38 pages)

- PCI-7256 (48 pages)

- PCI-7250 (48 pages)

- LPCI-7250 (48 pages)

- PCI-7396 (65 pages)

- PCI-7296 (59 pages)

- PCI-8554 (67 pages)

- PCIe-7350 (86 pages)

- PCIe-7300A (114 pages)

- PCIe-7200 (51 pages)

- PCI-7300A (112 pages)

- PCI-7300A (83 pages)

- PCI-7200 (96 pages)

- cPCI-7300 (82 pages)

- cPCI-7300 (83 pages)