Do dma in continuous mode, Figure 3-11: di timing diagram – ADLINK PCIe-7360 User Manual

Page 48

38

Operations

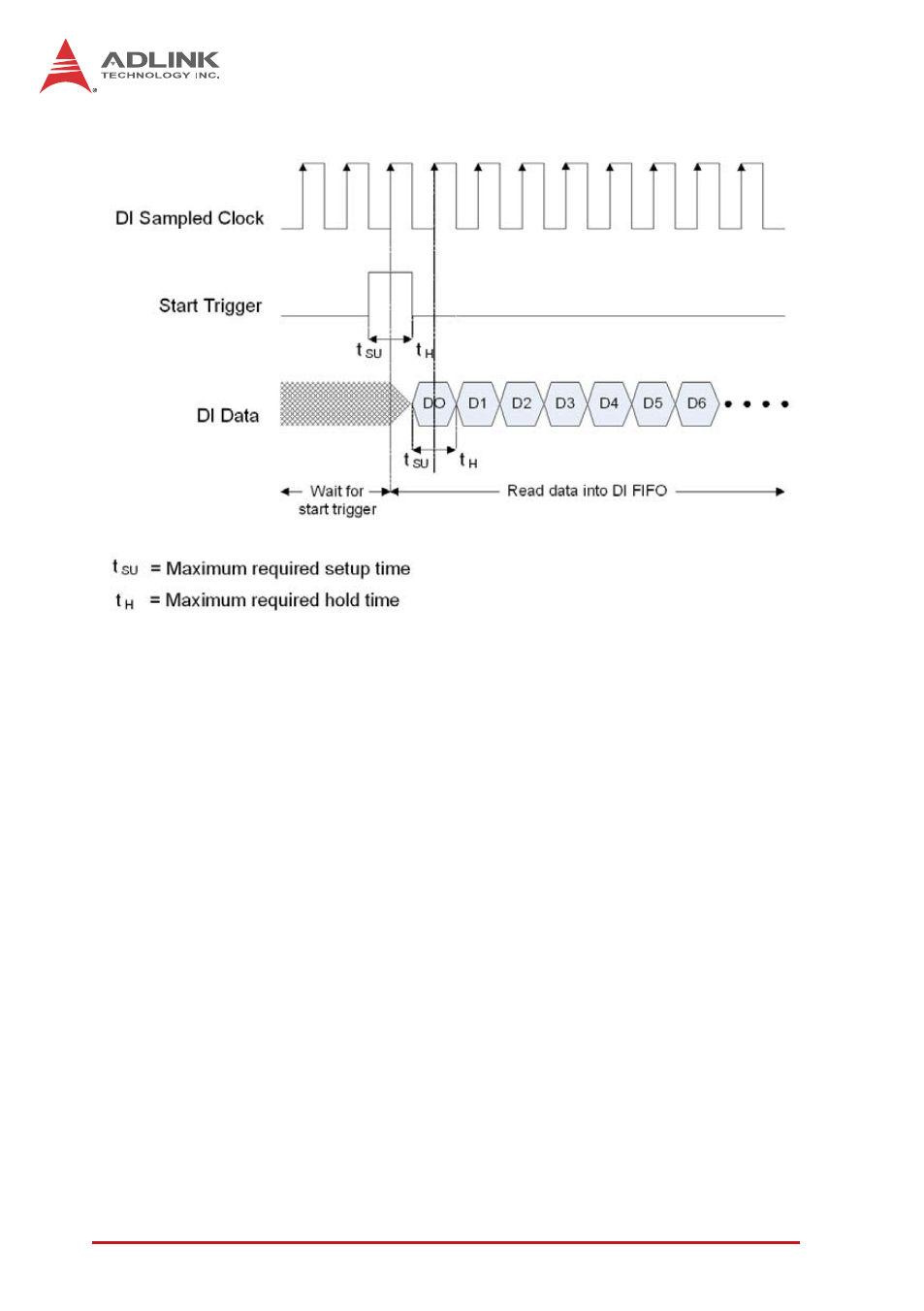

Figure 3-11: DI Timing Diagram

DO DMA in Continuous Mode

For the DO pattern generation operation in continuous mode,

PCIe-7360 card can generate digital data to external devices at a

specific update clock rate (DO sample clock). DO sample clock

can be selected from internal or external clock source. The opera-

tion sequences are listed as follows:

Steps:

X

Define DO port configuration (32/24/16/8-bits data width)

X

Define DO logic level configuration (3.3/2.5/1.8 V)

X

Define DO sample clock configuration (internal/external)

Z

If choose internal sample clock, you can define sampling

clock rate to be 100MHz/n (n = 1 to 65535)

Z

If choose external sample clock, the phase shift function

is available when external clock rate is 20 to 100 MHz.

X

Define DO exporting sample clock configuration (AFI6/SMB

CLK out)

- USB-1901 (84 pages)

- USB-1210 (54 pages)

- USB-2401 (60 pages)

- USB-7230 (50 pages)

- USB-2405 (56 pages)

- DAQe-2010 (92 pages)

- DAQe-2204 (100 pages)

- DAQe-2213 (94 pages)

- DAQe-2501 (74 pages)

- PXI-2010 (84 pages)

- PXI-2020 (60 pages)

- PXI-2501 (62 pages)

- cPCI-9116 (98 pages)

- ACL-8112 Series (93 pages)

- ACL-8112 Series (94 pages)

- ACL-8112 Series (92 pages)

- ACL-8216 (75 pages)

- ACL-8111 (61 pages)

- PCM-9112+ (10 pages)

- PCM-9112+ (94 pages)

- cPCI-6216V (47 pages)

- ACL-6126 (28 pages)

- ACL-6128A (40 pages)

- PCM-6308V+ (4 pages)

- PCM-6308V+ (52 pages)

- PCI-7444 (82 pages)

- PCI-7434 (48 pages)

- PCI-7234 (56 pages)

- PCI-7260 (66 pages)

- PCI-7258 (38 pages)

- PCI-7256 (48 pages)

- PCI-7250 (48 pages)

- LPCI-7250 (48 pages)

- PCI-7396 (65 pages)

- PCI-7296 (59 pages)

- PCI-8554 (67 pages)

- PCIe-7350 (86 pages)

- PCIe-7300A (114 pages)

- PCIe-7200 (51 pages)

- PCI-7300A (112 pages)

- PCI-7300A (83 pages)

- PCI-7200 (96 pages)

- cPCI-7300 (82 pages)

- cPCI-7300 (83 pages)