Achronix Speedster22i PCIe User Manual

Page 61

UG030, April 26, 2013

61

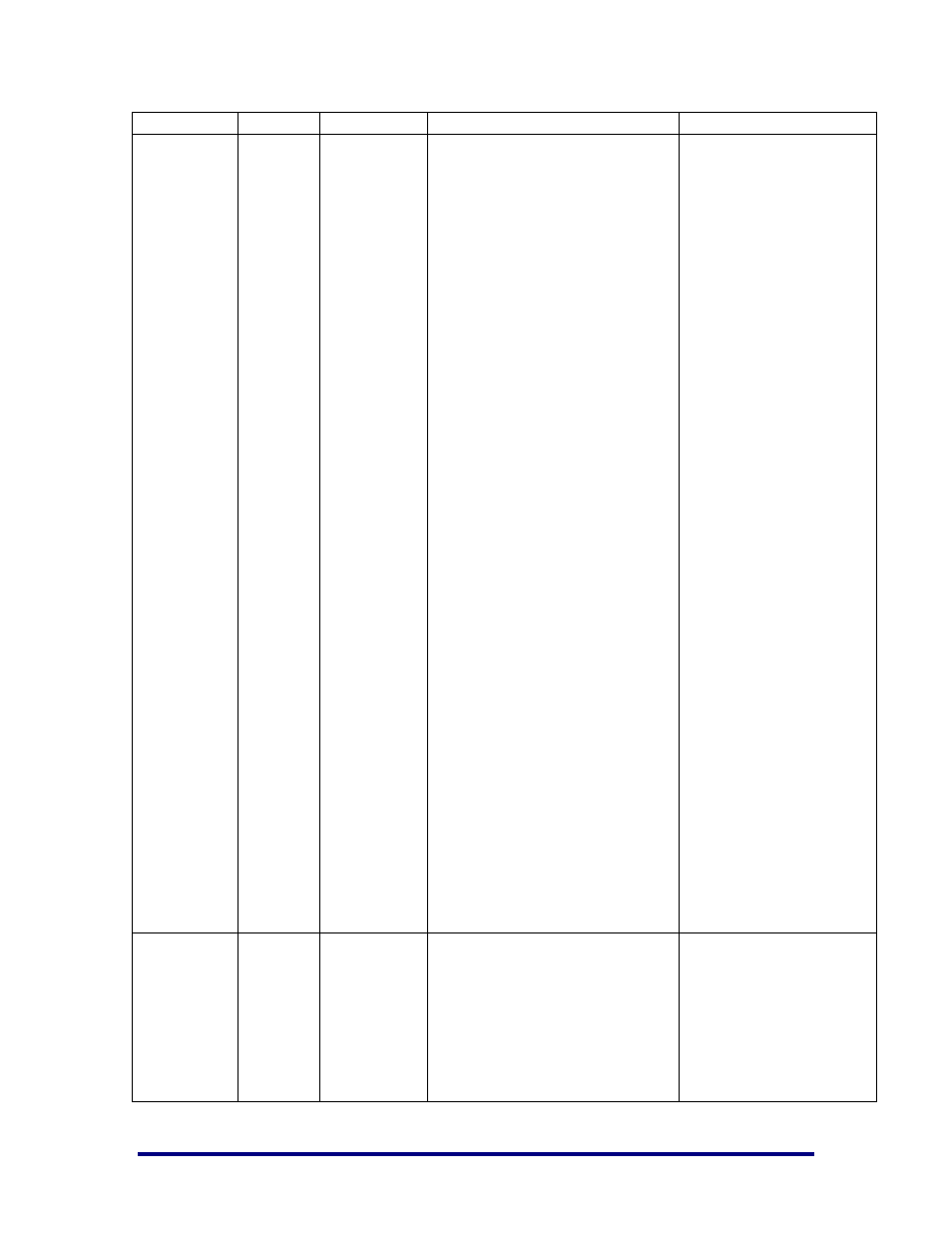

Field Name

Default

Values

Description

Verilog Parameter

it is required to map the MSI-X

Table and MSI-X PBA into a

dedicated, aligned 4 KByte (OS

page size) or larger (8 KByte

recommended) address region of

the shared BAR.

MSI-X Table BIR[2:0] indicates to

system software which one of a

function’s Base Address registers

is used to map the function’s

MSI-X Table into Memory Space.

For a 64-bit BAR, the BAR

location that contains the lower

32-bits of address is indicated. For

example if the MSI-X table is

located in a 64-bit Memory Space

implemented via {BAR1, BAR0}

then Table BIR is set to 000

(BAR0). For example if the MSI-X

table is located in a 32-bit

Memory Space implemented via

BAR2 then Table BIR is set to 010

(BAR2). MSI-X Table BIR[2:0] is

set as follows:

000 – Base Address

Register 0 (0x10)

001 – Base Address

Register 1 (0x14)

010 – Base Address

Register 2 (0x18)

011 – Base Address

Register 3 (0x1C)

100 – Base Address

Register 4 (0x20)

101 – Base Address

Register 5 (0x24)

110 – Reserved

111 – Reserved

MSI-X Table

Offset

0x0C00

29-Bit hex

MSI-X Table Offset[31:3] - Value

to place into MSI-X Capability :

Table Offset field.

MSI-X Table BIR indicates which

Base Address Register contains

the MSI-X Table. See MSI-X Table

BIR description for additional

information.

CFG_CONTROL_MSI_X_

TABLE_OFFSET