Achronix Speedster22i PCIe User Manual

Page 41

UG030, April 26, 2013

41

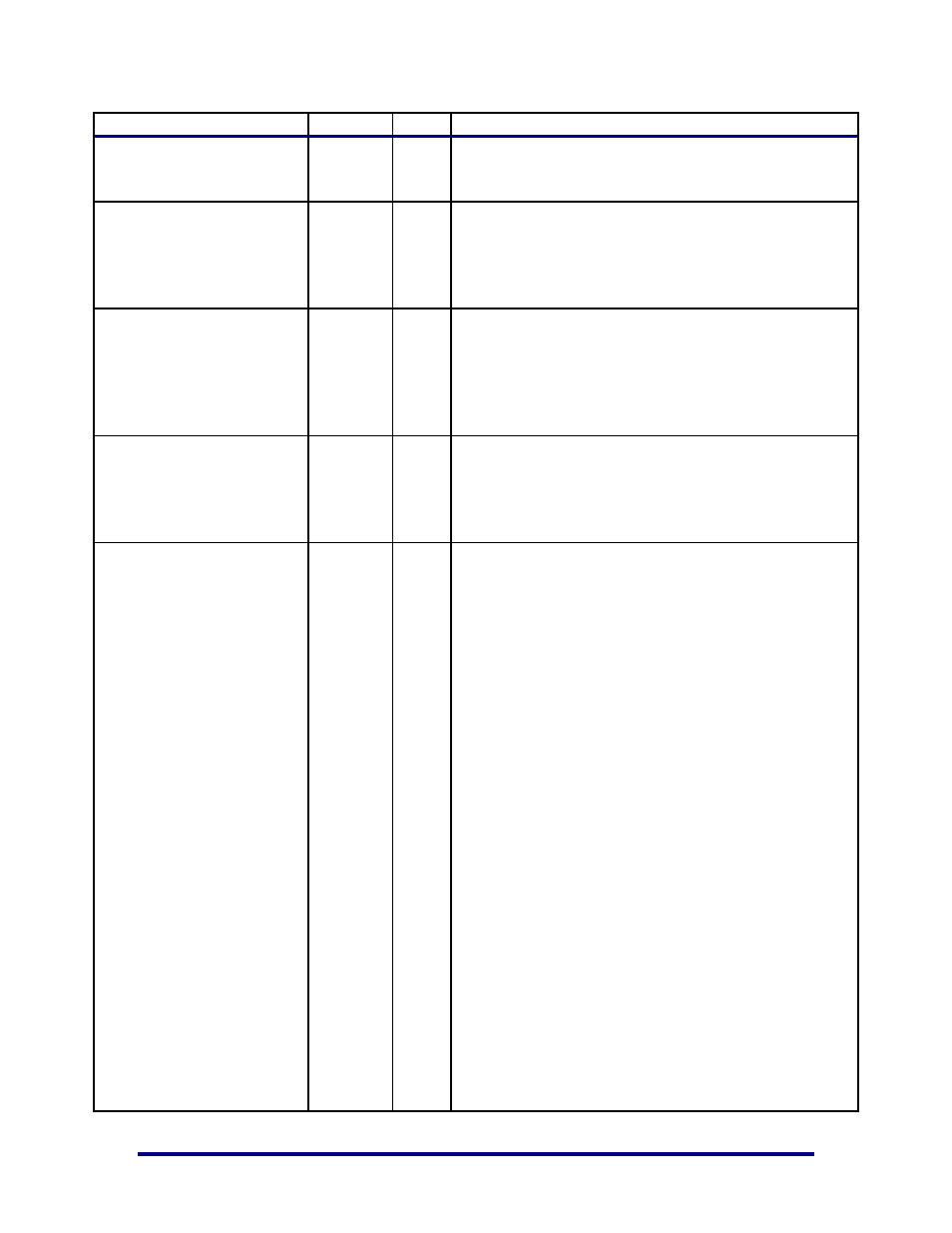

Pin Name

Direction Clock

Description

useful for user designs to monitor power state changes

and to determine if they want to assert a PME event to

change the power state back to D0.

pm_l1_enter

Output

Set to 1 by the core for 1 clock when the core begins the

process of entering the L1 link state; 0 otherwise. The

core enters L1 whenever Power_State is programmed to

a value other than D0=-00 and core support for L1 has

been enabled (see mgmt_cfg_constants [377]).

pm_l1_exit

Output

Set to 1 by the core for 1 clock when the core exits the L1

link state back to L0; 0 otherwise. The core exits L1

under system control or in response to a user PME

request via pm_d3cold_n_pme_assert assertion.

pm_l1_enter and pm_l1_exit are informational and can

be ignored for most applications.

pm_l2_enter

Output

Set to 1 by the core for 1 clock when the core begins the

process of entering the L2 link state; 0 otherwise. The

core begins the process of entering L2 whenever a

PM_Turn_Off message is received and core support for

L2 has been enabled (see mgmt_cfg_constants[376]).

pm_l2_enter_ack

Input

The system transmits a PME_Turn_Off message to

Endpoints to instruct them to prepare for power down.

When a PME_Turn_Off message is received, a

PME_TO_Ack message must be transmitted to inform

the system that the Endpoint is ready for power down.

The core provides the option for the core or user to

control the timing of the PME_TO_Ack message

generation via

Disable_Auotmatic_PME_TO_Ack_Message_Generation

== mgmt_cfg_constants[382]:

0 – PME_TO_Ack message is transmitted

automatically in response to PME_Turn_Off

message; In this case, tie pm_l2_enter_ack = 0.

1 – PME_TO_Ack message is transmitted when

the user asserts pm_l2_enter_ack == 1. An

assertion of pm_l2_enter must be followed by

an assertion of pm_l2_enter_ack as soon as the

user design can prepare for power down. The

user‟s device driver should already have been

informed of, and allowed the transition to L2, so

only information required to be stored that the

driver does not have access to (such as registers

that need to be maintained through D3cold)

should need to be stored at this point.

Systems are permitted to implement a time out

mechanism to power down the system if a