Achronix Speedster22i PCIe User Manual

Page 35

UG030, April 26, 2013

35

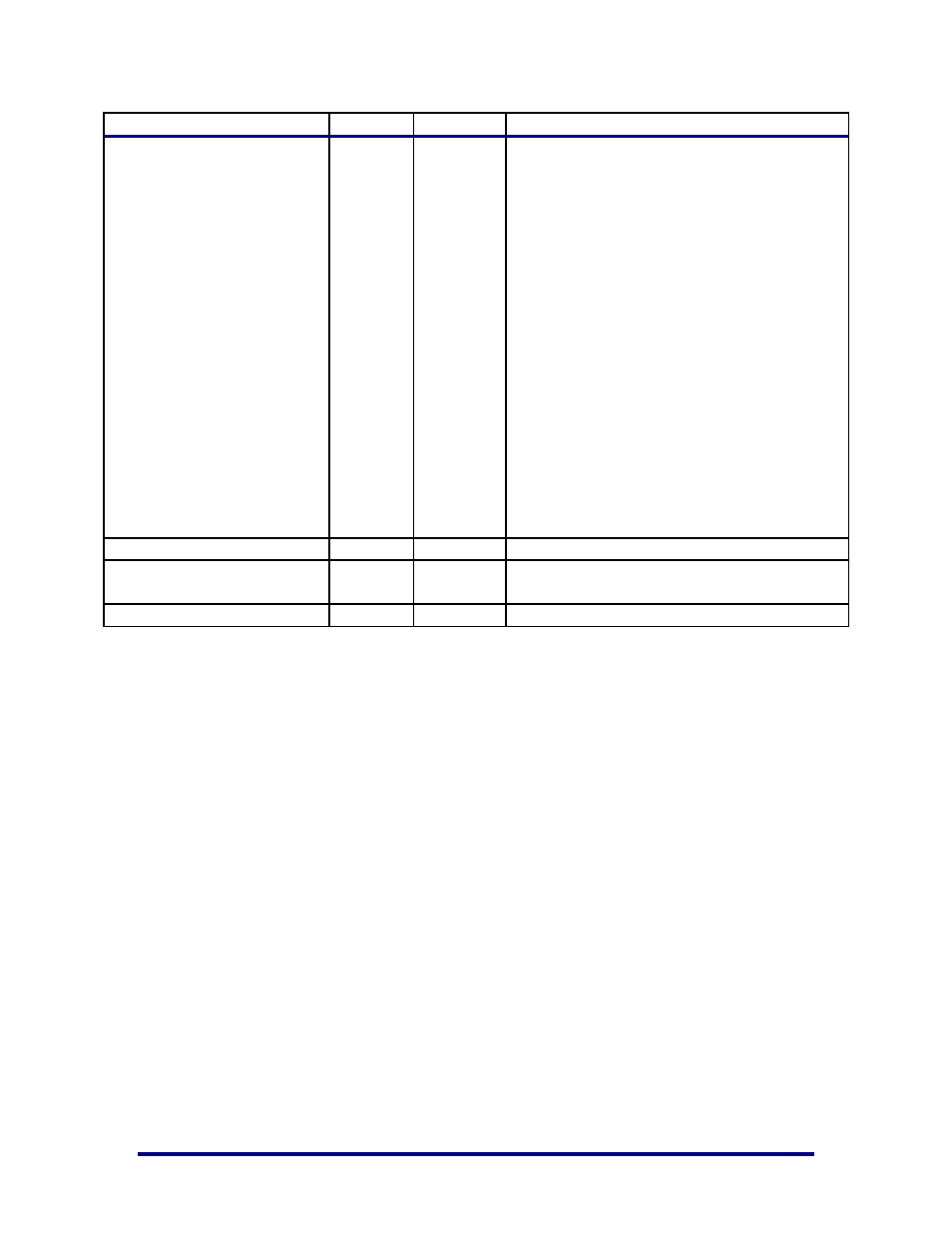

Port Name

Direction

Clock

Description

global Function Mask (mgmt_cfg_status[1182])

or by the per vector Mask Bit (MSI-X Table

entry bit 96) then that vector is masked and

cannot be requested by asserting

mgmt_interrupt_msix_req until the vector is

unmasked. For each clock cycle that

mgmt_interrupt_msix_req == 1 and

mgmt_interrupt_msix_ack ==1, the core

transmits a MSI-X Interrupt by transmitting a

Memory Write containing the address and

data value contained in the provided

mgmt_interrupt_msix_vector[127:0]. System

software may not allocate as many MSI-X

interrupt vectors as requested by the design so

user hardware and software must be designed

to share interrupts if required. The user

hardware design must take into account any

interrupt sharing and always provide a valid,

system-software-allocated vector.

bypass_interrupt_msix_ack

Output

bypass_clk

bypass_interrupt_msix_vector

[127:0]

Input

bypass_clk

bypass_enable

Input

bypass_clk DMA Bypass interface enable