Achronix Speedster22i PCIe User Manual

Page 59

UG030, April 26, 2013

59

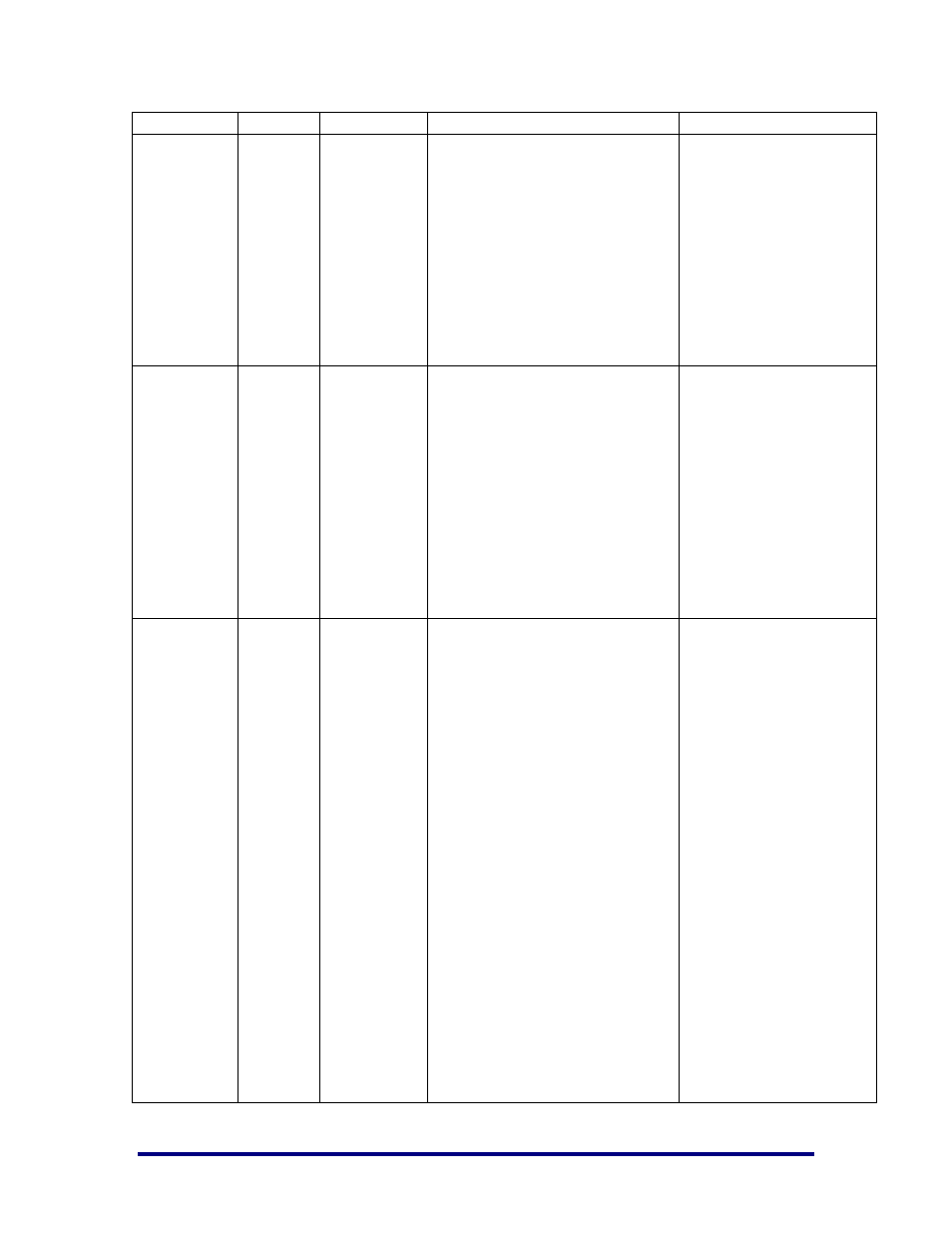

Field Name

Default

Values

Description

Verilog Parameter

initializing this field to “010”).

The encoding is defined as

follows:

000 – Request 1 vector

001 - Request 2 vectors

010 - Request 4 vectors

011 - Request 8 vectors

100 - Request 16 vectors

101 - Request 32 vectors

110 - Reserved

111 - Reserved

MSI-X

Capability

Disable

No

Yes, No

MSI-X Capability Disable – (1)

Disable MSI-X Capability; (0)

Enable MSI-X Capability; when

(1) the core’s MSI-X Capability is

removed from the Configuration

Registers Capabilities List, MSI-X

Interrupt functionality is

disabled, and it will not be

possible to send MSI-X interrupts;

this bit only affects core

configurations that support MSI-

X

CFG_CONTROL_MSI_X_

CAPABILITY_DISABLE

MSI-X Table

Size

31

0 to 2^11

MSI-X Table Size[10:0] – Value to

place into MSI-X Capability:

Table Size field.

MSI-X functionality requires the

user design to implement the

MSI-X Table in Memory Space.

MSI-X Table Size[10:0] is set to

indicate the number of MSI-X

Table entries (Interrupt Vectors)

implemented. MSI-X Table Size is

read by software to determine the

size of the MSI-X Table.

MSI-X Table Size is set to the

number of MSI-X Table entries

(Interrupt Vectors) supported by

the user’s MSI-X Table minus 1.

For example if 32 Table entries

(Interrupt Vectors) are supported,

then MSI-X Table Size[10:0] ==

0x01F.

Each MSI-X Table entry (Interrupt

Vector) requires 4 DWORDs to

store a 64-bit address, 32-bit data

CFG_CONTROL_MSI_X_

TABLE_SIZE