Axi master interface – Achronix Speedster22i PCIe User Manual

Page 37

UG030, April 26, 2013

37

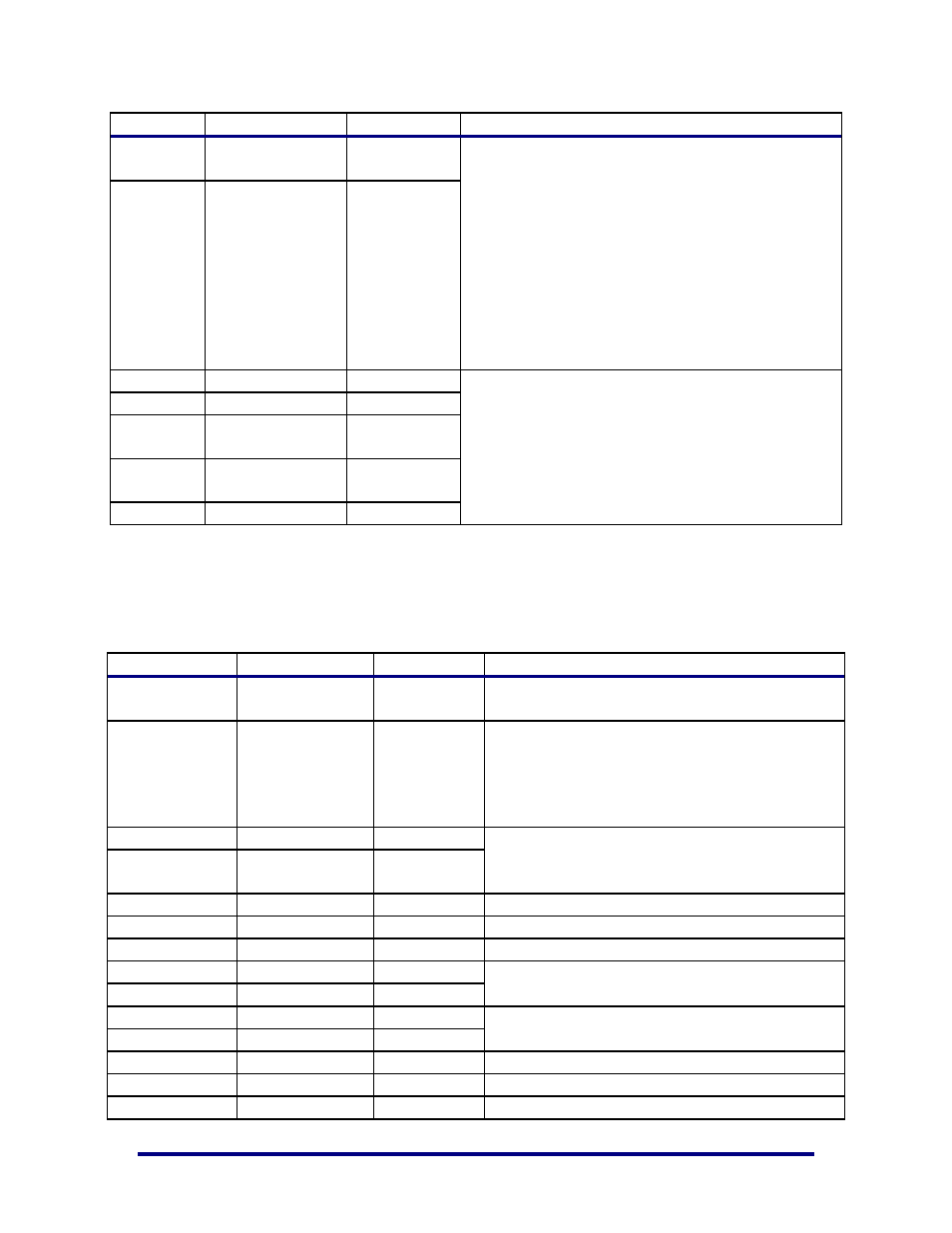

Pin Name

Direction

Clock

Description

t_arlen

[3:0]

Output

t_aclk

target_awregion and target_arregion indicate PCI

Express Base Address Region hit information:

• 0: BAR0

• 1: BAR1

• 2: BAR2

• 3: BAR3

• 4: BAR4

• 5: BAR5

• 6: Expansion ROM

• 7: Reserved

t_arsize

[2:0]

Output

t_aclk

t_rvalid

Input

t_aclk

Read Data Channel; space is reserved in the master

to receive data from all outstanding read requests,

so t_rready is always 1

t_rready

Output

t_aclk

t_rdata

[127:0]

Input

t_aclk

t_rresp

[1:0]

Input

t_aclk

t_rlast

Input

t_aclk

AXI Master Interface

Table 5: Master Interface Pin Descriptions

Pin Name

Direction

Clock

Description

m_areset_n

Input

m_aclk

Active-low asynchronous assert, m_aclk-

synchronous de-assert reset

m_aclk

Input

AXI interface clock; may be a different clock than

the clock used on the PCI Express-side of the AXI

DMA Back-End Core; synchronization techniques

are used to enable support for a wide variety of

clock rates

m_awvalid

Input

m_aclk

A Write Address Channel transfer occurs when

m_awvalid == 1 and m_awready == 1

implemented

m_awready

Output

m_aclk

m_awaddr[15:0]

Input

m_aclk

Byte address of register to write

m_wdata [31:0]

Input

m_aclk

Data to write

m_wstrb [3:0]

Input

m_aclk

Byte enables for write

m_wvalid

Input

m_aclk

A Write Data Channel transfer occurs when

m_wvalid == 1 and m_wready == 1

m_wready

Output

m_aclk

m_bvalid

Output

m_aclk

A Write Response Channel transfer occurs when

m_bvalid == 1 and m_bready == 1

m_bready

Input

m_aclk

m_bresp [1:0]

Output

m_aclk

Status of write request: 0 – Successful; 1, 2,3 Error

m_araddr [15:0]

Input

m_aclk

Byte address of register to read

m_rvalid

Output

m_aclk

A Read Response Channel transfer occurs when