Achronix Speedster22i PCIe User Manual

Page 44

UG030, April 26, 2013

44

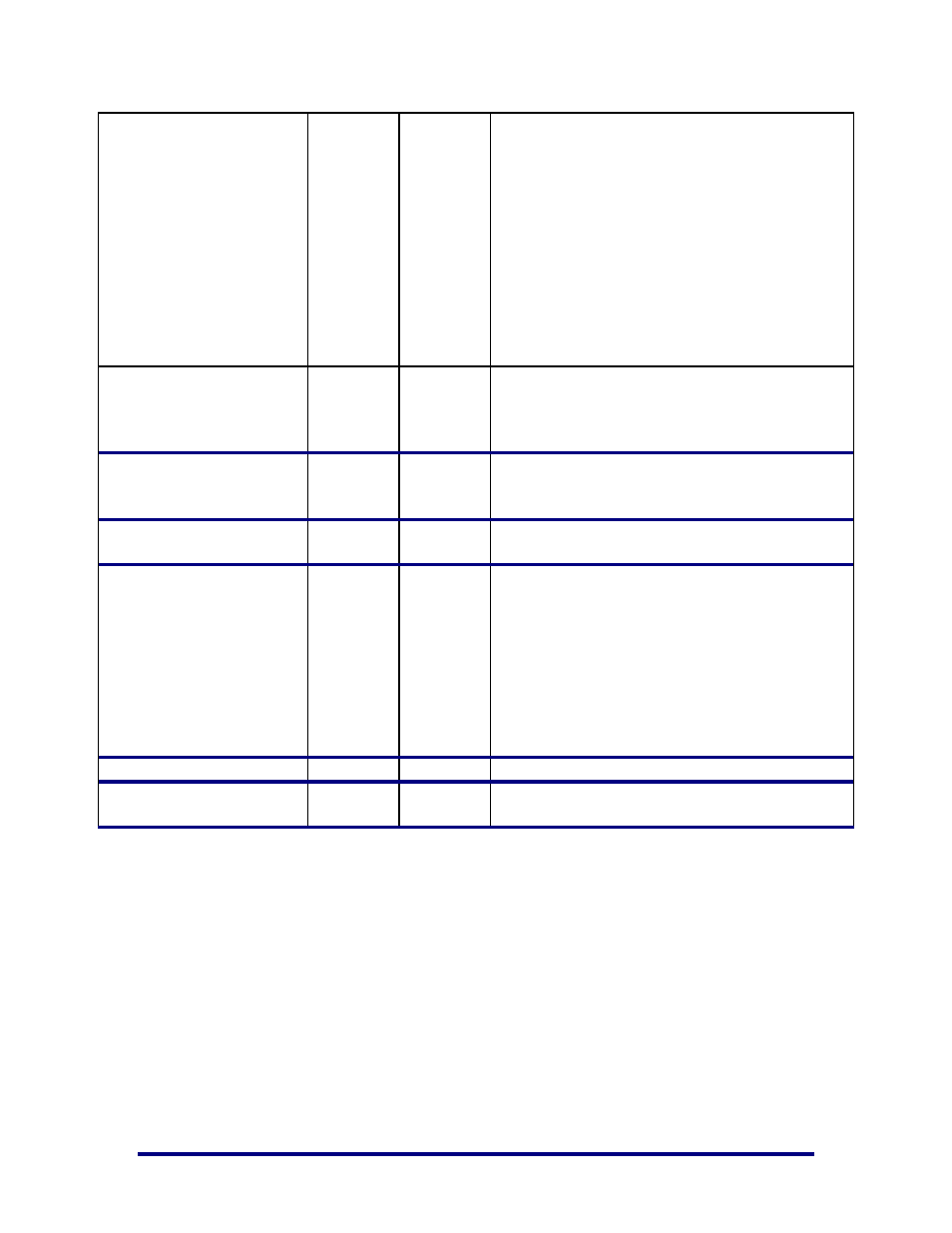

core_cfg_exp_addr [11:2]

Input

core_clk

Configuration register being addressed for a

write; all accesses are DWORD aligned (address

bits 1:0 are always 00); {cfg_exp_wr_addr [11:2],

00} addresses in the range of 0x000 to 0x0BC and

0x100 to 0x1FC are handled exclusively by the

core . Addresses between 0x0C0 and 0xFC and

0x200 and 0xFFC are forwarded to the

Configuration Register Expansion Interface for

termination by user logic. This interface is active

for all Configuration Requests, even those that

target core configuration regions, so a full address

decode must be completed.

core_cfg_exp_wr_en

Input

core_clk

When cfg_exp_wr_en is high, the Configuration

Register addressed by cfg_exp_addr must be

written with core_cfg_exp_wr_data conditioned

by cfg_exp_wr_ be byte enables.

core_cfg_exp_wr_data[31:0]

Input

core_clk

Data to write to the addressed Configuration

Register; must be conditionally applied using the

cfg_exp_wr_be byte enables.

core_cfg_exp_wr_be[3:0]

Input

core_clk

Active high byte enables; 1 == write byte; 0 == do

not write byte

core_cfg_exp_rd_en

Input

core_clk

Configuration register read enable; when

core_cfg_exp_rd_en == 1, core_cfg_exp_addr is

valid and specifies the address of the

configuration register that is being read; 1 clock

following core_cfg_exp_rd_en == 1,

core_cfg_exp_rd_data must be valid and contain

the contents of the register accessed by

core_cfg_exp_addr; core_cfg_exp_rd_data must

be held until the next read request

core_cfg_exp_rd_data[31:0]

Output

core_clk

core_cfg_exp_rd_val

Output

core_clk

This signal indicate core_cfg_exp_rd_data is

valid.