Major interfaces, Axi target interface, Figure 3: axi target interface – Achronix Speedster22i PCIe User Manual

Page 10

UG030, April 26, 2013

10

Major Interfaces

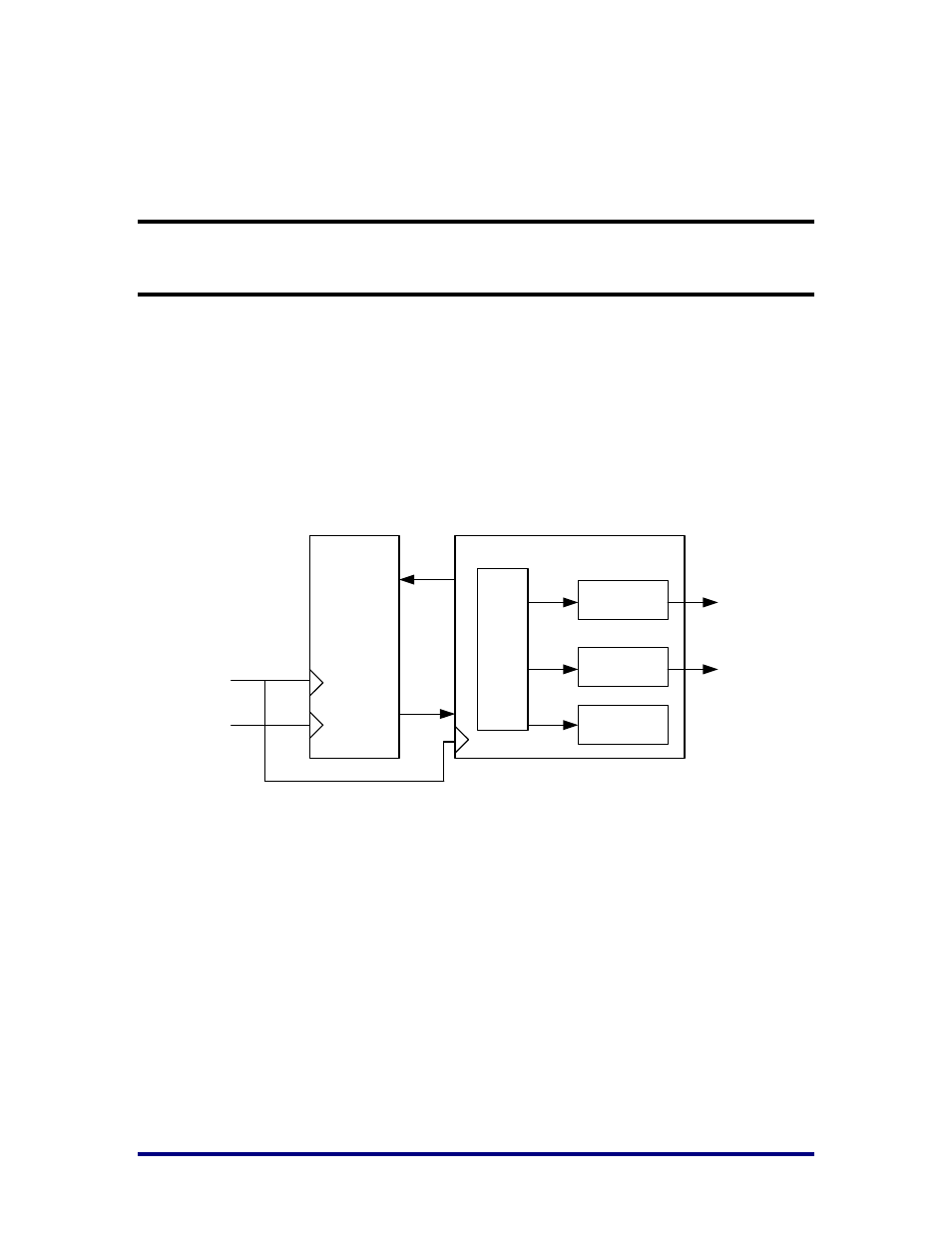

AXI Target Interface

The AXI Target Interface implements AXI3/AXI4 Master Protocol. Write and

read requests received via PCI Express (from remote PCI Express masters)

that target AXI regions of enabled Base Address or Expansion ROM regions

are forwarded to the AXI Target Interface for completion. Accesses to

registers inside the AXI DMA Back-End Core are handled by the core and do

not appear on the AXI Target Interface.

shows the interface connection between AXI Target Interface and

Fabric Controller:

clk

target_aclk

RX

TX

PCIe-Core

Target Controller (Fabric Core)

SDRAM

Controller

Internal

Registers

Internal

SRAM

Target

Control

SDRAM

GPI/O

Figure 3: AXI Target Interface

enables another PCI Express master device (such as a

CPU) to access external SDRAM, internal SRAM, and General Purpose I/O.

In this design each of the three interfaces is assigned a memory Base Address

Register. The Target Control module steers the incoming packets from PCIe-

Core to the appropriate destination based upon the Base Address Register

that was hit and formats the data (if needed) to the appropriate width. The

design receives Posted Request packets containing write requests and data

and performs the writes on the addressed interface. The design receives

Non-Posted Request packets containing read requests, performs the read on

the addresses interface, and then transmits one or more Completion packets

containing the requested read data.

The AXI Target Interface implements write-read ordering to maintain

coherency for PCI Express transactions (see