Achronix Speedster22i PCIe User Manual

Page 26

UG030, April 26, 2013

26

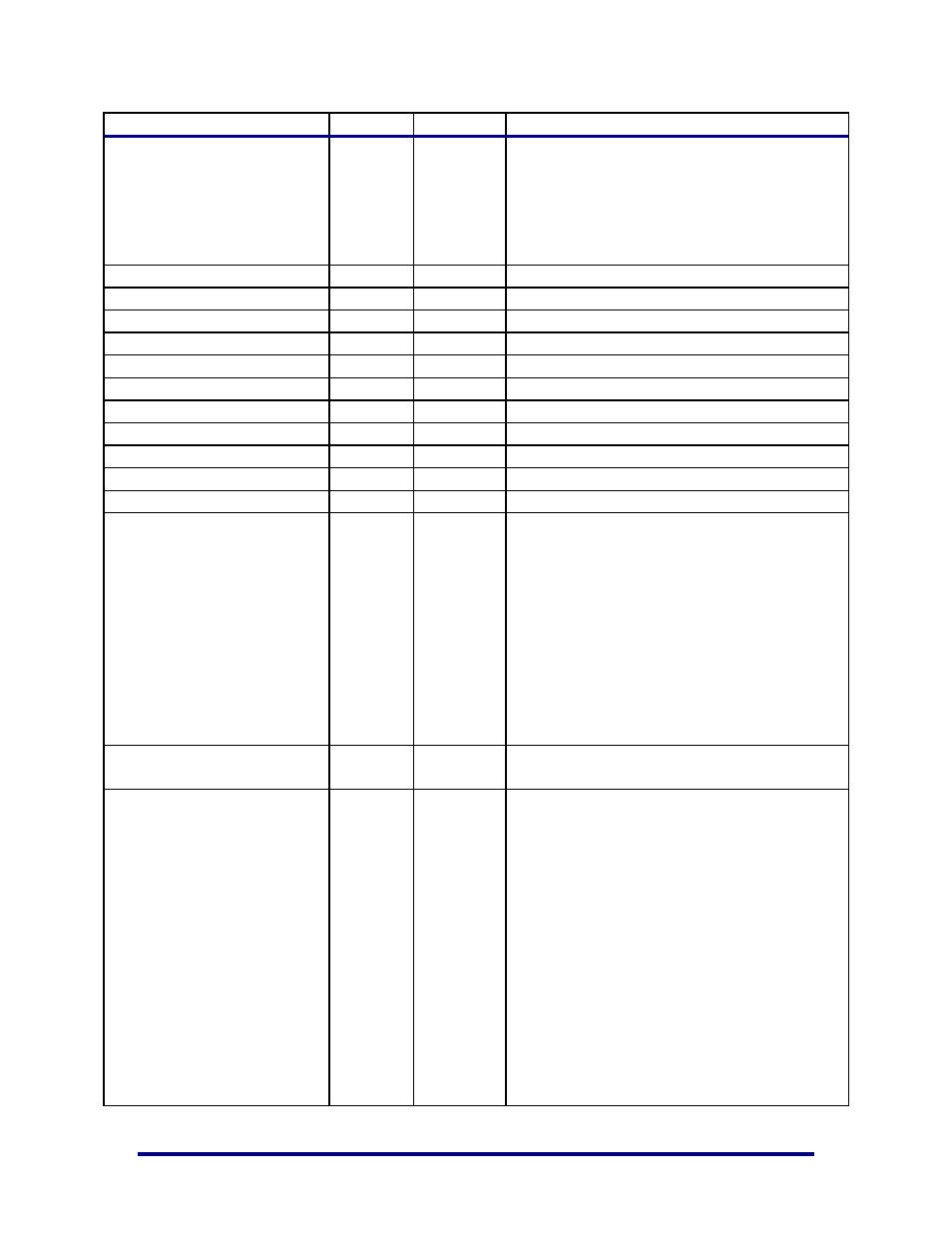

Port Name

Direction

Clock

Description

clocking (majority of open systems). The

required 600 ppm maximum clock difference

between devices may not be met when Spread

Spectrum clocking is in use unless both devices

in the link are using the same Spread

Spectrum-modulated clock reference.

i_sbus_clk

Input

i_sbus_clk Serial-Bus clock

i_sbus_req

Input

i_sbus_clk SBUS interface request

i_sbus_sw_rst

Input

i_sbus_clk Soft reset to the SBUS interface

i_sbus_data[1:0]

Input

i_sbus_clk SBUS write data

o_sbus_ack

Output

i_sbus_clk SBUS acknowledgment

o_sbus_rdata[1:0]

Output

i_sbus_clk SBUS read data

bypass_clk

Input

bypass_clk DMA Bypass clock

bypass_rst_n

Input

bypass_clk DMA Bypass Reset

bypass_tx_valid

Input

bypass_clk DMA Bypass Tx Data Valid

bypass_tx_ready

Output

bypass_clk DMA Bypass Tx ready

bypass_tx_almost_full

Output

bypass_clk DMA Bypass Tx Data Fifo almost full

bypass_tx_sop

Input

bypass_clk Start of packet indicator and packet transmit

request; set == 1 coincident with the first

vc0_tx_data word in each packet. vc0_tx_sop

may not be asserted until the user is ready to

provide the entire packet with the minimum

possible timing of the core’s vc0_tx_en

assertions.

The user may wait state the transmit interface

only between packets; the user may choose to

hold off on transmitting a packet by not

asserting vc0_tx_sop.

bypass_tx_eop

Input

bypass_clk End of packet indicator; set == 1 coincident

with the last vc0_tx_data word in each packet.

bypass_tx_data[127:0]

Input

bypass_clk Packet data to transfer; vc0_tx_data must be

valid from the assertion of vc0_tx_sop until the

packet is fully consumed with the assertion of

vc0_tx_eop == vc0_tx_en == 1. The core may

assert and de-assert vc0_tx_en at any time, so

the user must ensure that vc0_tx_sop,

vc0_tx_eop, and vc0_tx_data are always valid.

Packet data must comprise a complete

Transaction Layer packet as defined by the PCI

Express Specification including the entire

packet header, data payload, and optional TLP

Digest (ECRC). The core adds the necessary

STP/END/EDB framing, Sequence Number,

LCRC, and for cores with ECRC support,

ECRC as part of its Data Link Layer