Achronix Speedster22i PCIe User Manual

Page 54

UG030, April 26, 2013

54

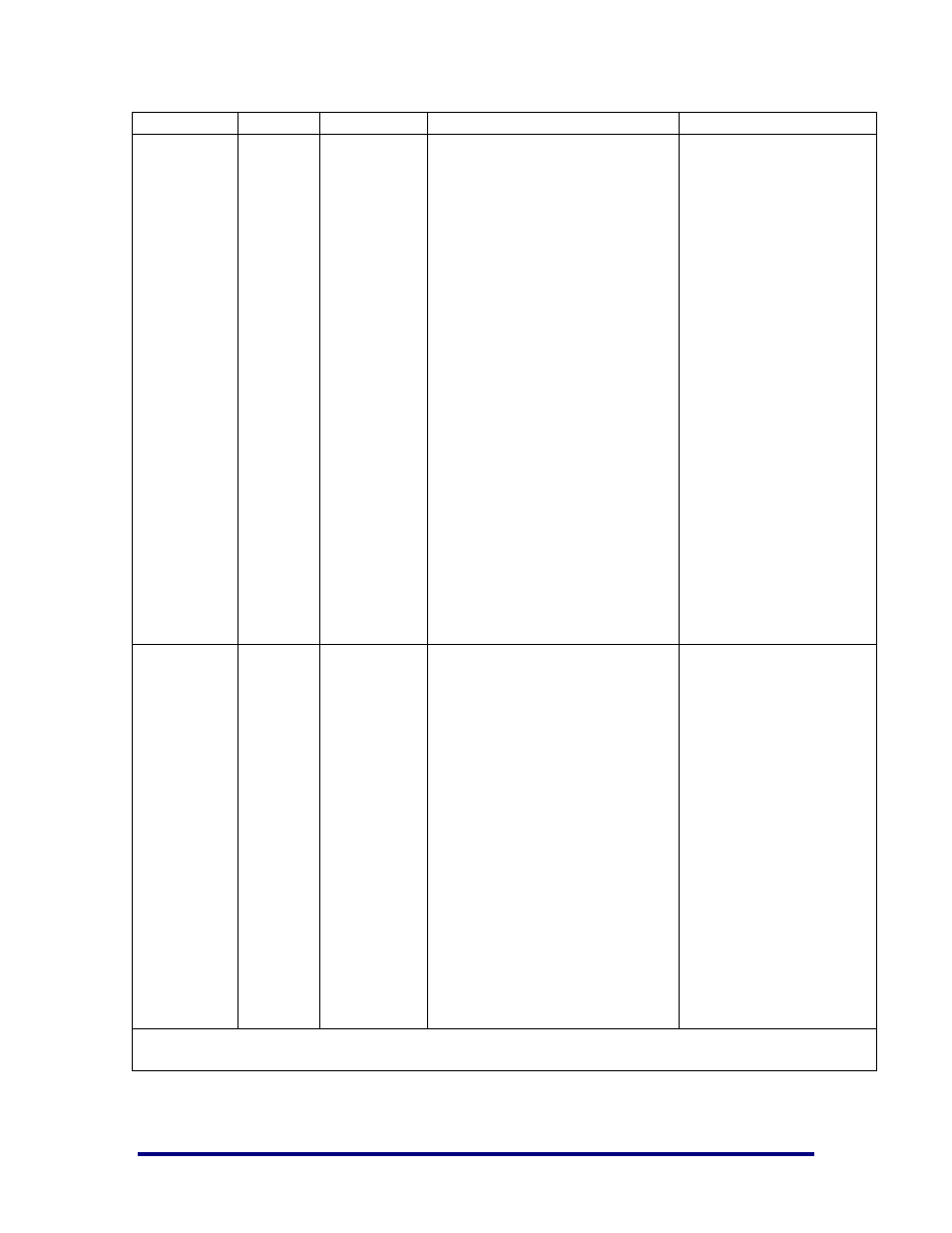

Field Name

Default

Values

Description

Verilog Parameter

against the L1 Exit Latencies

reported (see below) by all

components comprising the data

path from this Endpoint to the

Root Complex Root Port to

determine whether ASPM L1

entry can be used with no loss of

performance.” Note that the

amount of buffering refers to the

user application buffering. Users

should set this field in accordance

with how long a delay is

acceptable for their application.

000 - Maximum of 1 μs

001 - Maximum of 2 μs

010 - Maximum of 4 μs

011 - Maximum of 8 μs

100 - Maximum of 16 μs

101 - Maximum of 32 μs

110 - Maximum of 64 μs

111 - No limit

Non-Endpoints must

hard wire this field to

000.

L1 Exit

Latency

More

than

64us

L1 Exit Latency – Length of time

required to complete transition

from L1 to L0:

000 - Less than 1μs

001 - 1 μs to less than 2 μs

010 - 2 μs to less than 4 μs

011 - 4 μs to less than 8 μs

100 - 8 μs to less than 16

μs

101 - 16 μs to less than 32

μs

110 - 32 μs-64 μs

111 - More than 64 μs

Exit latencies may be significantly

increased if the PCI Express

reference clocks used by the two

devices in the link are common or

separate.

CFG_CONTROL_PCIE_L

INK_CAP_L1_EXIT_LAT

ENCY

Advanced Features