Management interface – Achronix Speedster22i PCIe User Manual

Page 40

UG030, April 26, 2013

40

Pin Name

Direction

Clock

Description

c2s_rvalid [1:0]

Input

c2s_aclk

FIFO DMA: Read Data Channel implements AXI4-

Stream Slave protocol using c2s_rdata(tdata),

c2s_ruserstrb(tkeep), c2s_rlast(tlast), c2s_rvalid(tvalid),

and c2s_rready(tready). NULL (TKEEP[i] == 0) bytes

only permitted at the end of a stream; position bytes not

implemented; optional TSTRB, TID, and TDEST not

implemented; interleaving of streams is not supported; a

new stream may only start after the prior stream

finishes; c2s_ruserstatus is a non-standard AXI signal,

which must be valid when c2s_rlast (tlast) == 1 &

c2s_rvalid (tvalid) == 1, that is used to update the

UserStatus[63:0] value in the last Descriptor of the

packet; optional signal which may be used to pass

information on a per packet basis from user hardware to

user software; c2s_ruserstatus is only valid for FIFO

DMA; if unused, tie to 0

Addressable DMA: Read Data Channel implements

AXI3/AXI4 Master protocol; non-standard AXI ports

c2s_ruserstrb & c2s_ruserstatus are unused and must be

tied to 0.

c2s_rready [1:0]

Output

c2s_aclk

c2s_rdata [255:0]

Input

c2s_aclk

c2s_rresp [3:0]

Input

c2s_aclk

c2s_rlast [1:0]

Input

c2s_aclk

c2s_ruserafull

[1:0]

Output

c2s_aclk

c2s_ruserstrb

[31:0]

Input

c2s_aclk

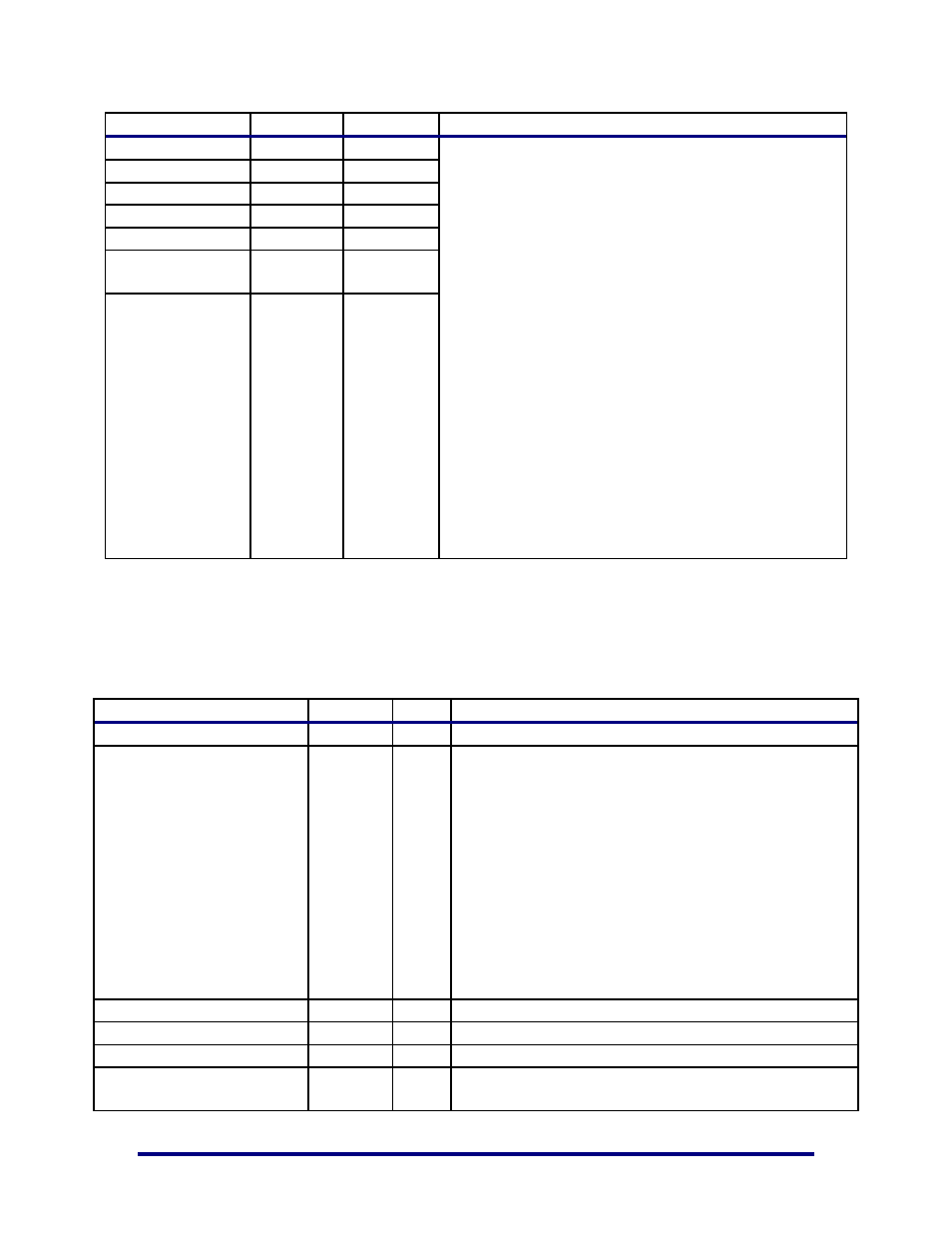

Management Interface

Table 8: Management Interface Port Descriptions

Pin Name

Direction Clock

Description

mgmt_pl_link_up_o

Output

Physical Layer Status; (1) Up; (0) Down

mgmt_cfg_id [15:0]

Output

Every PCI Express device is assigned a unique ID which

it must use to generate Requests and to respond with

Completion packets. The ID is assigned by system

software on every Configuration Write, but practically

does not change during regular operation. The core

holds the current ID assigned by system software and

makes it available as mgmt_cfg_id. mgmt_cfg_id must

be used in place of the Requestor ID packet header field

when generating Requests and must be used in place of

the Completer ID packet header field when generating

Completions. See PCI Express Base Specification, Rev 2.0,

Section 2.2.6.2 for additional detail.

mgmt_transactions_pending

Input

Management transaction pending from user.

user_interrupt

Input

User Interrupt to the PCIe core.

mgmt_rp_leg_int_o [3:0]

Output

Legacy interrupts generated from Interrupt Messages.

pm_power_state [1:0]

Output

Value of the core’s Power Management Capability:

Power_State [1:0] Configuration register. This register is