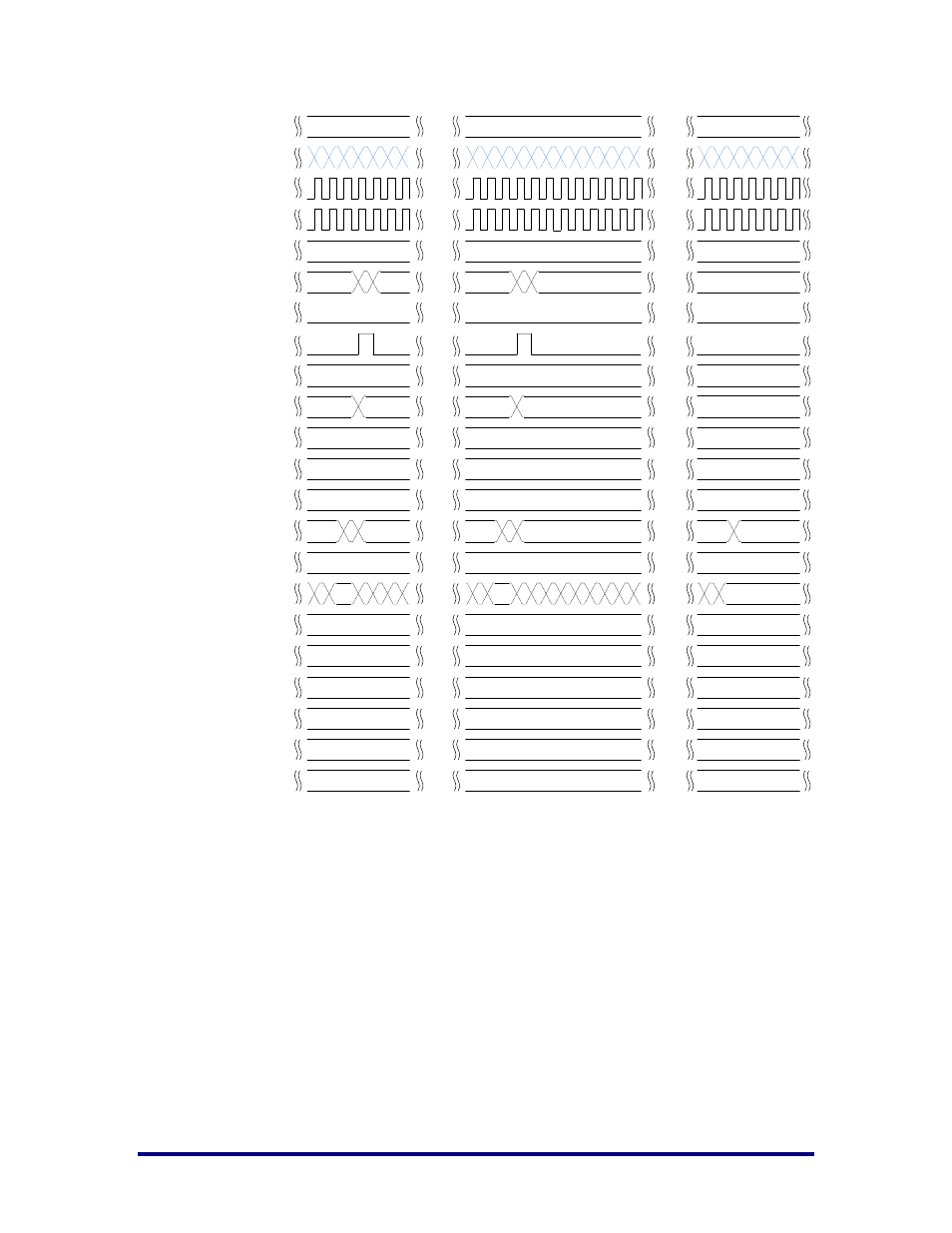

Packet dma descriptor format, Figure 6 – Achronix Speedster22i PCIe User Manual

Page 15

UG030, April 26, 2013

15

2'h0

s2c_aclk[1:0]

St0

s2c_aclk[1]

St0

s2c_aclk[0]

2'h3

s2c_fifo_addr_n[1:0]

2'h0

s2c_awvalid[1:0]

St0

s2c_awvalid[1]

St0

s2c_awvalid[0]

2'h3

s2c_awready[1:0]

s2c_awready[71:0]

8'h0f

s2c_awlen[7:0]

2'h0

s2c_awusereop[1:0]

6'h24

s2c_awsize[5:0]

s2c_wdstrb[31:0]

2'h0

s2c_wlast[1:0]

2'h0

s2c_wusereop[1:0]

2'h0

s2c_bvalid[1:0]

2'h3

s2c_bready[1:0]

4'h0

s2c_bresp[3:0]

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

s2c_areset_n[1:0]

2'h3

s2c_wdata[255:0]

s2c_wready[1:0]

2'h3

s2c_wvalid[1:0]

2'h1

*fc

7b00

00 0000

*3c

3

3

3

0f

0

24

1

3

0000 ffff

0

0

0

0

3

00 0000 0000

3

3

3

3

0

0

0

0

0

0001 7c00

00 0000 0000 0001 7d00

00 0000 0000 0001 7d00

0f

0f

0

24

0

24

1

0

3

3

0000 ffff

0

0

0

0

3

0000 ffff

0

0

0

0

3

1

1

1

...

...

...

Figure 6: Timing Diagram for System-to-Card DMA Interface

Packet DMA Descriptor Format

A 256-bit (32-byte) Descriptor is defined for Packet DMA which contains the

Control fields required to specify a packet copy operation and the Status

fields required to specify the success/failure of the packet copy operation.

The Descriptor is split into Control and Status fields:

Control fields are fields that are written into the Descriptor by

software before the Descriptor is passed to the DMA Engine. Control

fields specify to the DMA Engine what copy operation to perform.

Status fields are fields that are written into the Descriptor by the

DMA Engine after completing the DMA operation described in the