Achronix Speedster22i PCIe User Manual

Page 46

UG030, April 26, 2013

46

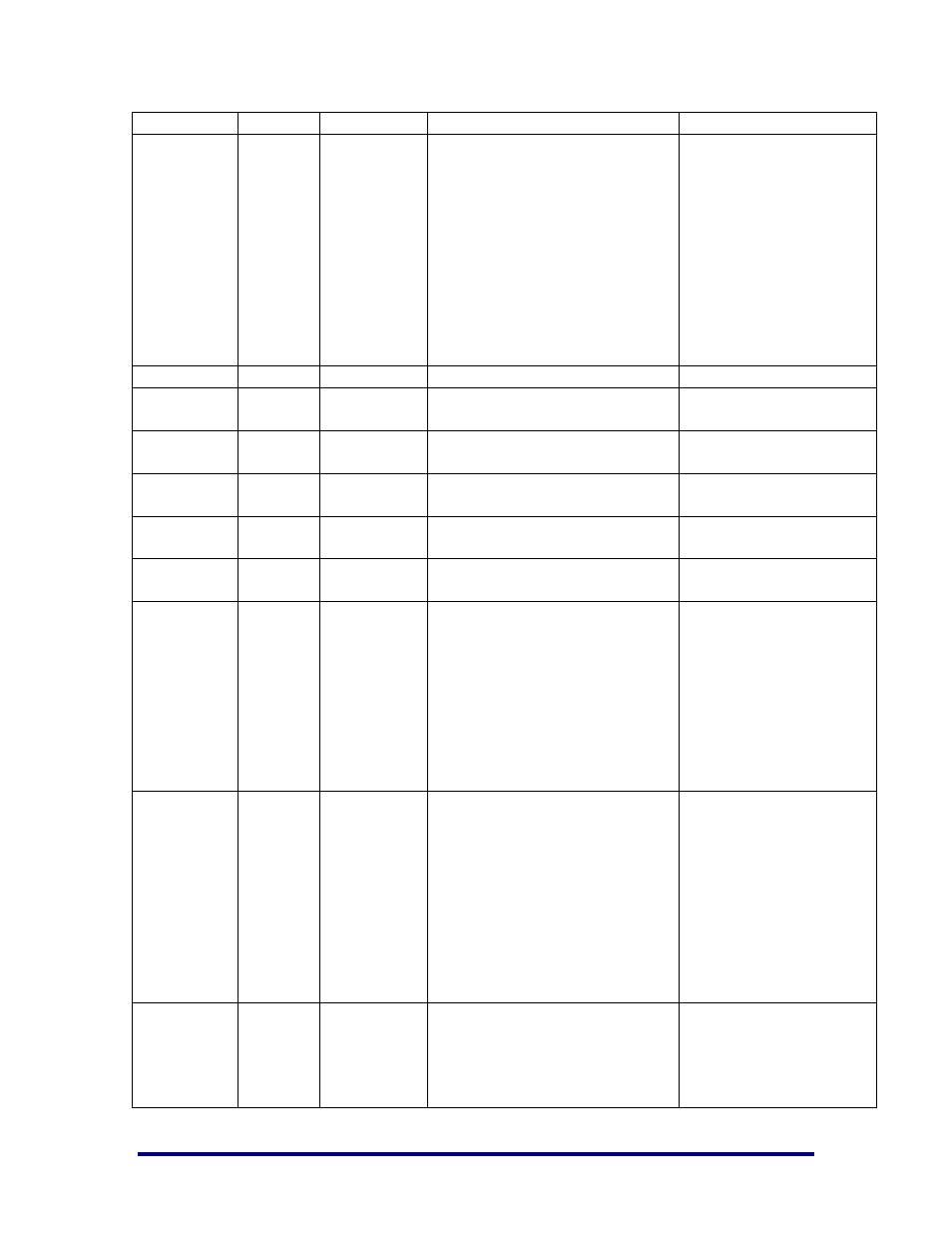

Field Name

Default

Values

Description

Verilog Parameter

CFG_CONSTANTS_SUP

PORT_8GTS = 0;

}

CFG_CONSTANTS_SUP

PORT_5GTS = 1;

} else {

CFG_CONSTANTS_SUP

PORT_8GTS = 0;

CFG_CONSTANTS_SUP

PORT_5GTS = 0;

}

PCIe Width

8

1, 4, 8

Number of SerDes lanes

NUM_OF_LANES

Device ID

0xE004

0x0000 –

0xFFFF

PCIe Device ID

CFG_CONSTANTS_DEV

ICE_ID

Subsystem

ID

0xE004

Subsystem ID

CFG_CONSTANTS_SUB

SYSTEM_ID

Revision ID

0x04

Revision ID

CFG_CONSTANTS_REVI

SION_ID

Vendor ID

0x19AA

Vendor ID

CFG_CONSTANTS_VEN

DOR_ID

Subsystem

Vendor ID

0x19AA

Subsystem Vendor ID

CFG_CONSTANTS_SUB

SYSTEM_VENDOR_ID

Class Code

0x118000

Class Code[23:0] – Value returned

when the Class Code

Configuration Register is read.

Must be set to the correct value

for the type of device being

implemented; see PCI Local Bus

Specification Revision 2.3 Appendix

D for details on setting Class

Code.

CFG_CONSTANTS_CLA

SS_CODE

Operating

Mode

Endpoint Endpoint,

Upstream

Switch Port,

Downstream

Switch Port

CFG_CONSTANTS_SWI

TCH_PORT_MODE ,

CFG_CONSTANTS_ROO

T_PORT_MODE

2’b11 – Upstream Switch

Port

2’b10 – Downstream

Switch Port

2’b00 – Endpoint

Root Port ID

0x0000

Root Port ID – This 16 bit field is

used to define the ID used for

PCIe Requester ID and Completer

ID when the core is operating as a

Downstream Port (Root Port,

CFG_CONSTANTS_ROO

T_PORT_ID