System-to-card engine interface – Achronix Speedster22i PCIe User Manual

Page 38

UG030, April 26, 2013

38

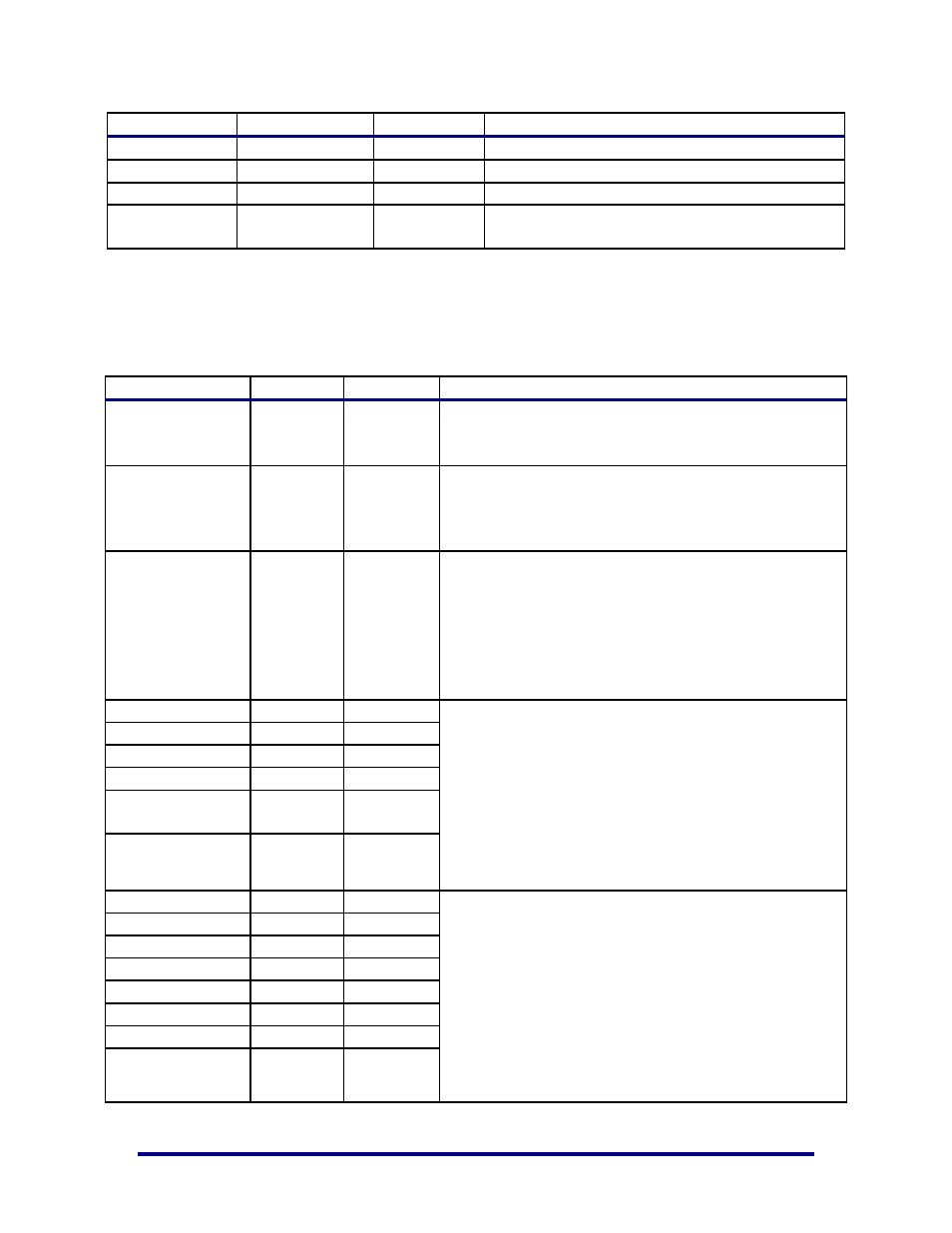

Pin Name

Direction

Clock

Description

m_rready

Input

m_aclk

m_rvalid == 1 and m_rready == 1

m_rdata [31:0]

Output

m_aclk

Data read

m_rresp [1:0]

Output

m_aclk

Status of read request: 0 – Successful; 1, 2,3 Error

m_interrupt

[4:0]

Output

m_aclk

System-to-Card Engine Interface

Table 6: System-to-Card Interface Port Descriptions

Pin Name

Direction

Clock

Description

s2c_areset_n

Output

s2c_aclk

Active-low asynchronous assert, s2c_aclk synchronous

de-assert reset; asserted when the DMA Engine has been

reset by software or by PCI Express reset

s2c_aclk [1:0]

Input

s2c_aclk

AXI interface clock; may be a different clock than the

clock used on the PCI Express-side of the AXI DMA

Back-End Core; synchronization techniques are used to

enable support for a wide variety of clock rates

s2c_fifo_addr_n

[1:0]

Input

s2c_aclk

Interface AXI Protocol Selection:

1 – FIFO DMA using AXI4-Stream Protocol

0 – Addressable DMA using AXI3/AXI4

Protocol

This port selects the interface protocol and affects the

operation of the remaining ports

s2c_awvalid [1:0]

Output

s2c_aclk

FIFO DMA: Write Address Channel is unused; tie

s2c_awready == 1 and ignore s2c_aw* outputs

Addressable DMA: Write Address Channel; Optional

AWBURST, AWLOCK, AWCACHE, AWPROT are not

implemented; AWBURST is always incrementing-

address burst; cache, protected, and exclusive accesses

not supported; s2c_awusereop is a non-standard AXI

signal that when 1 indicates that this is the final write

request of a DMA packet transfer

s2c_awready [1:0]

Input

s2c_aclk

s2c_awaddr [71:0]

Output

s2c_aclk

s2c_awlen [7:0]

Output

s2c_aclk

s2c_awusereop

[1:0]

Output

s2c_aclk

s2c_awsize [5:0]

Output

s2c_aclk

s2c_wvalid [1:0]

Output

s2c_aclk

FIFO DMA: Write Data Channel implements AXI4-

Stream Master protocol using s2c_wdata(tdata),

s2c_wstrb(tkeep), s2c_wlast(tlast), s2c_wvalid(tvalid),

and s2c_wready(tready); NULL (TKEEP == 0) bytes are

only placed at the end of a stream (packet); position

bytes not implemented; optional TSTRB, TID, and

TDEST not implemented; interleaving of streams is not

performed; a new stream will start only after the prior

stream finishes; s2c_wusercontrol is a non-standard AXI

signal, valid for the entire packet transfer (typically

s2c_wready [1:0]

Input

s2c_aclk

s2c_wdata [255:0]

Output

s2c_aclk

s2c_wstrb [31:0]

Output

s2c_aclk

s2c_wlast [1:0]

Output

s2c_aclk

s2c_wusereop

[1:0]

Output

s2c_aclk