Receiver, Asynchronous receiver, Synchronous receiver – Rainbow Electronics AT75C220 User Manual

Page 77: Receiver ready, Parity error, Framing error

AT75C220

77

Receiver

Asynchronous Receiver

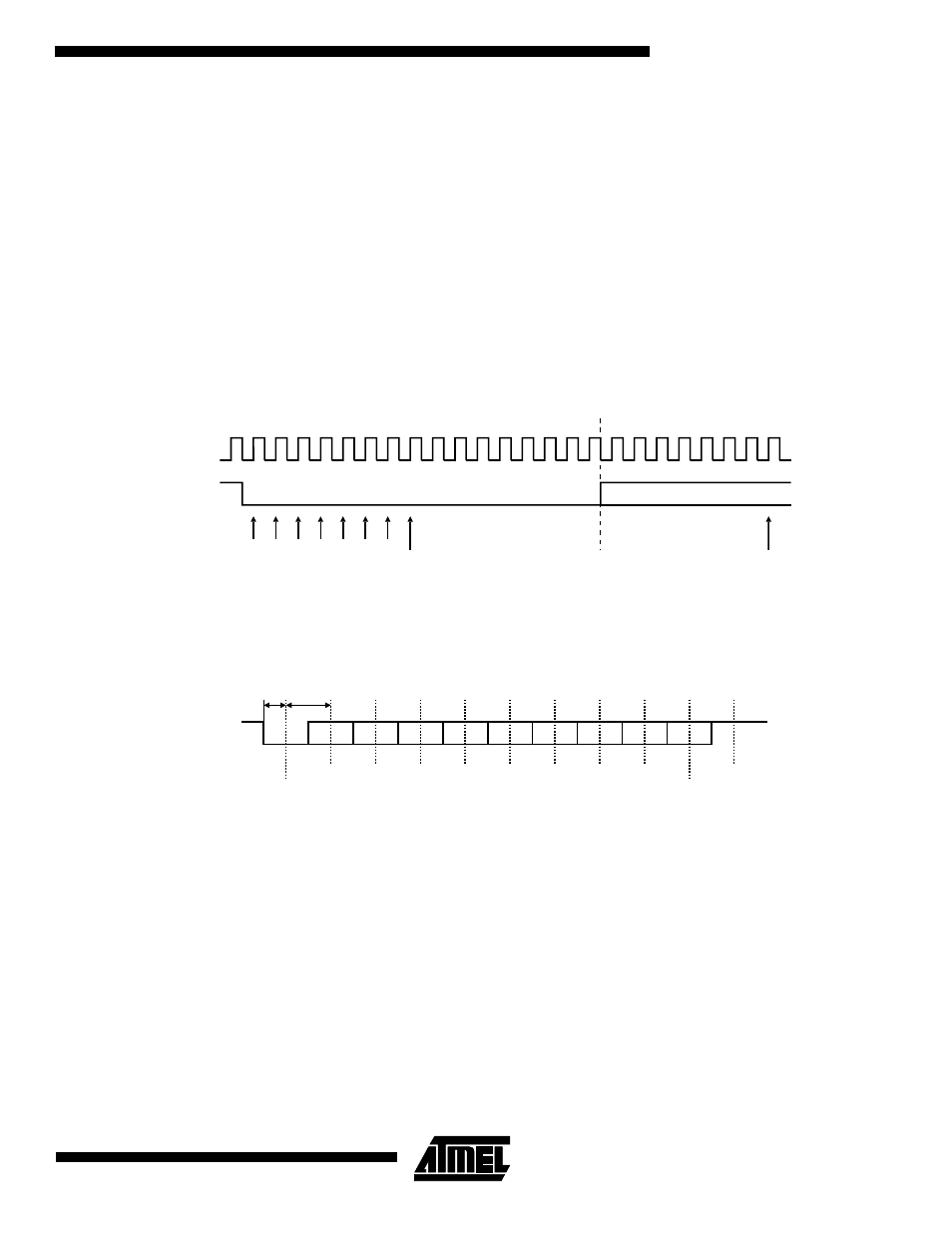

The USART is configured for asynchronous operation

when SYNC = 0 (bit 7 of US_MR). In asynchronous mode,

the USART detects the start of a received character by

sampling the RXD signal until it detects a valid start bit. A

low level (space) on RXD is interpreted as a valid start bit if

it is detected for more than seven cycles of the sampling

clock, which is 16 times the baud rate. Hence, a space

which is longer than 7/16 of the bit period is detected as a

valid start bit. A space which is 7/16 of a bit period or

shorter is ignored and the receiver continues to wait for a

valid start bit.

When a valid start bit has been detected, the receiver sam-

ples the RXD at the theoretical mid-point of each bit. It is

assumed that each bit lasts 16 cycles of the sampling clock

(1-bit period) so the sampling point is eight cycles (0.5-bit

periods) after the start of the bit. The first sampling point is

therefore 24 cycles (1.5-bit periods) after the falling edge of

the start bit was detected. Each subsequent bit is sampled

16 cycles (1-bit period) after the previous one.

Figure 17. Asynchronous Mode: Start Bit Detection

Figure 18. Asynchronous Mode: Character Reception

Synchronous Receiver

When configured for synchronous operation (SYNC = 1),

the receiver samples the RXD signal on each rising edge of

the baud rate clock. If a low level is detected, it is consid-

ered as a start. Data bits, parity bit and stop bit are sam-

pled and the receiver waits for the next start bit. See the

example in Figure 19.

Receiver Ready

When a complete character is received, it is transferred to

the US_RHR and the RXRDY status bit in US_CSR is set.

If US_RHR has not been read since the last transfer, the

OVRE status bit in US_CSR is set.

Parity Error

Each time a character is received, the receiver calculates

the parity of the received data bits in accordance with the

field PAR in US_MR. It then compares the result with the

received parity bit. If different, the parity error bit PARE in

US_CSR is set.

Framing Error

If a character is received with a stop bit at low level and

with at least one data bit at high level, a framing error is

generated. This sets FRAME in US_CSR.

16 x Baud

Rate Clock

RXD

True Start

Detection

D0

Sampling

D0

D1

D2

D3

D4

D5

D6

D7

RXD

True Start Detection

Sampling

Parity Bit

Stop Bit

Example: 8-bit, parity enabled 1 stop

1-bit

period

0.5-bit

periods