Sdram refresh, D figure 10. note, Figure 10 – Rainbow Electronics AT75C220 User Manual

Page 26

AT75C220

26

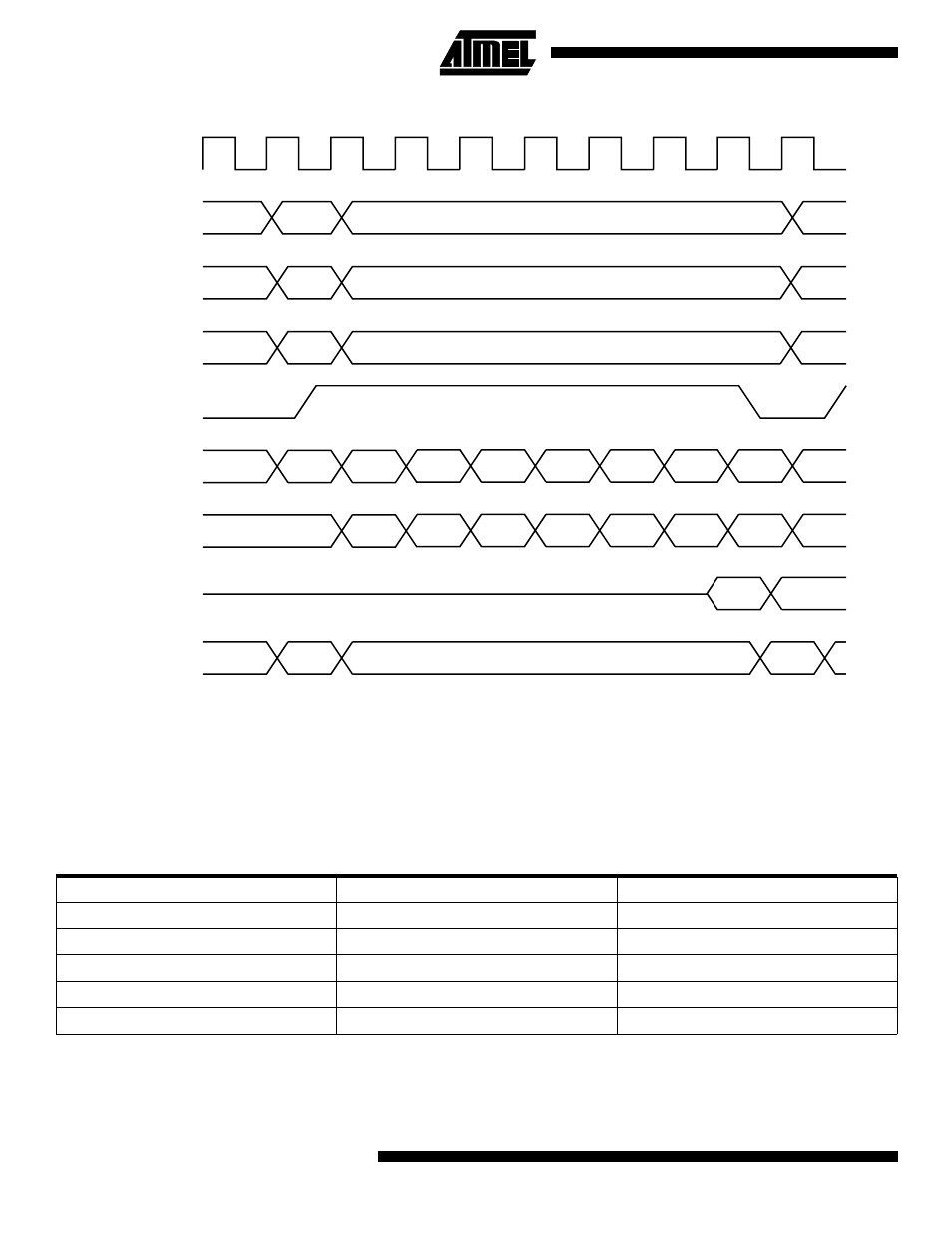

Figure 10. Read Showing a Single Access for a Non-sequential Read to a New Row

Writes can burst continuously until any of the following con-

ditions are achieved:

1.

The following access is a read.

2.

The following access is to a new row.

3.

The following access is non-sequential.

When any of these conditions occur, the write burst is bro-

ken and SDMC goes inactive.

SDRAM Refresh

Table 11 shows the counter values needed for a refresh

rate of 15.625 µs in the SDMC. As can be seen, at clock

speeds of 1 MHz and below it is unfeasible to maintain data

integrity in the SDRAM. Note that in low power modes it is

not a requirement to maintain data in the SDRAM.

BCLK

BA

BTRAN

BWAIT

SDRAM CMD

Addr

sdmc_data

BD

A0

A1

NSEQ

NSEQ

NOP

PRE

NOP

ACT

NOP

READ

NOP

NOP

BANK

ROW

COL0

COL1

D0

D0

INCR

INCR

hburst_h

NOP

Table 11. SDRAM Refresh Rates

Clock Speed (MHz)

Tick (us)

Counter Needed

40

0.25

62.5

8

1.25

12.5

1

10

1.5625

0.025

400

0.0390625

0.0032

3125

0.005

- RC2000 (2 pages)

- Т7023 (12 pages)

- Т7024 (20 pages)

- RC2200 (17 pages)

- RF01 (26 pages)

- RC1090 (17 pages)

- U3741BM (32 pages)

- U3742BM (32 pages)

- RAM01 (7 pages)

- RF22 (92 pages)

- RC1180-MBUS (28 pages)

- RFM01 (8 pages)

- RF12B (36 pages)

- RC1290 (17 pages)

- RC2300-ZNM (1 page)

- RF12 (31 pages)

- T48C862-R3 (107 pages)

- RF02 (24 pages)

- T48C862-R8 (107 pages)

- RFM12 (10 pages)

- U3745BM (29 pages)

- T5744 (19 pages)

- RFM12B (10 pages)

- U2745B (9 pages)

- T48C862-R4 (107 pages)

- RA01 (19 pages)

- T5754 (11 pages)

- U2741B (9 pages)

- RFM02 (8 pages)

- RC2100 (22 pages)

- RF модули диапазона ISM (4 pages)

- T5761 (35 pages)

- BTM -17х (5 pages)

- ATA8401 (12 pages)

- BTM -22х (7 pages)

- AT86RF231 (180 pages)

- ATA5575M1 (7 pages)

- AT88RF1354 (50 pages)

- ATA5812 (90 pages)

- AT86RF401 (50 pages)

- AT76C551 (77 pages)

- BTM -250 (6 pages)

- AT75C310 (132 pages)

- AT75C320 (13 pages)

- BTM -140 (6 pages)