Rainbow Electronics AT75C220 User Manual

Page 13

AT75C220

13

•

SA: Slow ARM Mode

On reset this field is low. In normal operating mode, if bit SA is set. The ARM clock is 34Mhz (i.e. the PLL value is

divided by 7). IF SA is not set the ARM clock is 40MHz (i..e the PLL divisor is 6). SA can be switched during low power

mode but should not be changed when LP is low.

•

LPCS: Low Power Clock Select

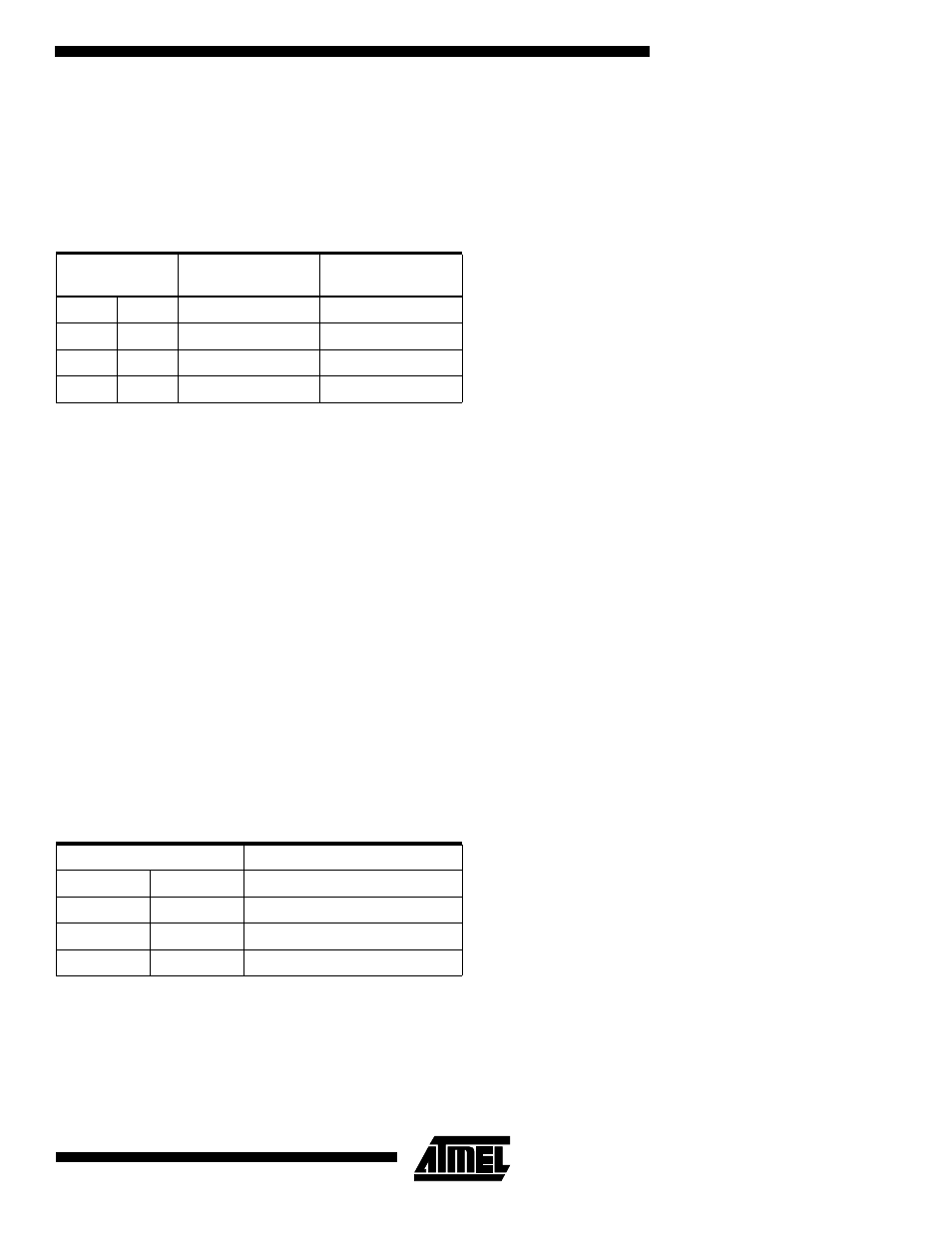

This field is used to select a slower clock frequency for the ARM system clock as per the table below.

•

SW1: Software Reset 1

Writing a 1 to this bit forces the SIAP into reset with RM set to 0.

•

SW2: Software Reset 2

Writing a 1 to this bit forces the SIAP into reset with RM set to 1.

•

DBA: OAKA Debug Mode

This flag resets low. To enter OAKA debug mode (specific pins are multiplexed out on functional pins), this bit should

be set.

•

CRA: CODECA Reset

This flag resets to active low so that the CODECA is held in reset. The CODECA is released from reset by asserting

this flag high.

•

IPOLTST: PLL Bias Adjustment

This can be used to tune the PLL if the bias current is not correct after manufacture.

•

ICP: PLL Charge Pump Current

This can be used to tune the PLL if it does not function with the default current of 2.5 µA.

•

INDIV

Input frequency range of PLL.

LPCS

Oscillator Clock

Divisor

ARM and Oak

System Clock

0

0

1

8 MHz

0

1

16

1 MHz

1

0

64

250 kHz

1

1

512

32 kHz

Bias Factor

15

IPOLTST

–

(

) 4

⁄

=

I

ICP

(

1

)

+

2.5

µA

×

=

INDIV

PLL Input Frequency Range

0

0

5 kHz to 40 MHz

0

1

40 MHz to 80 MHz

1

0

80 MHz to 160 MHz

1

1

160 MHz to 250 MHz