Peripheral memory map, Initialization, Reset pin – Rainbow Electronics AT75C220 User Manual

Page 10: Processor synchronization

AT75C220

10

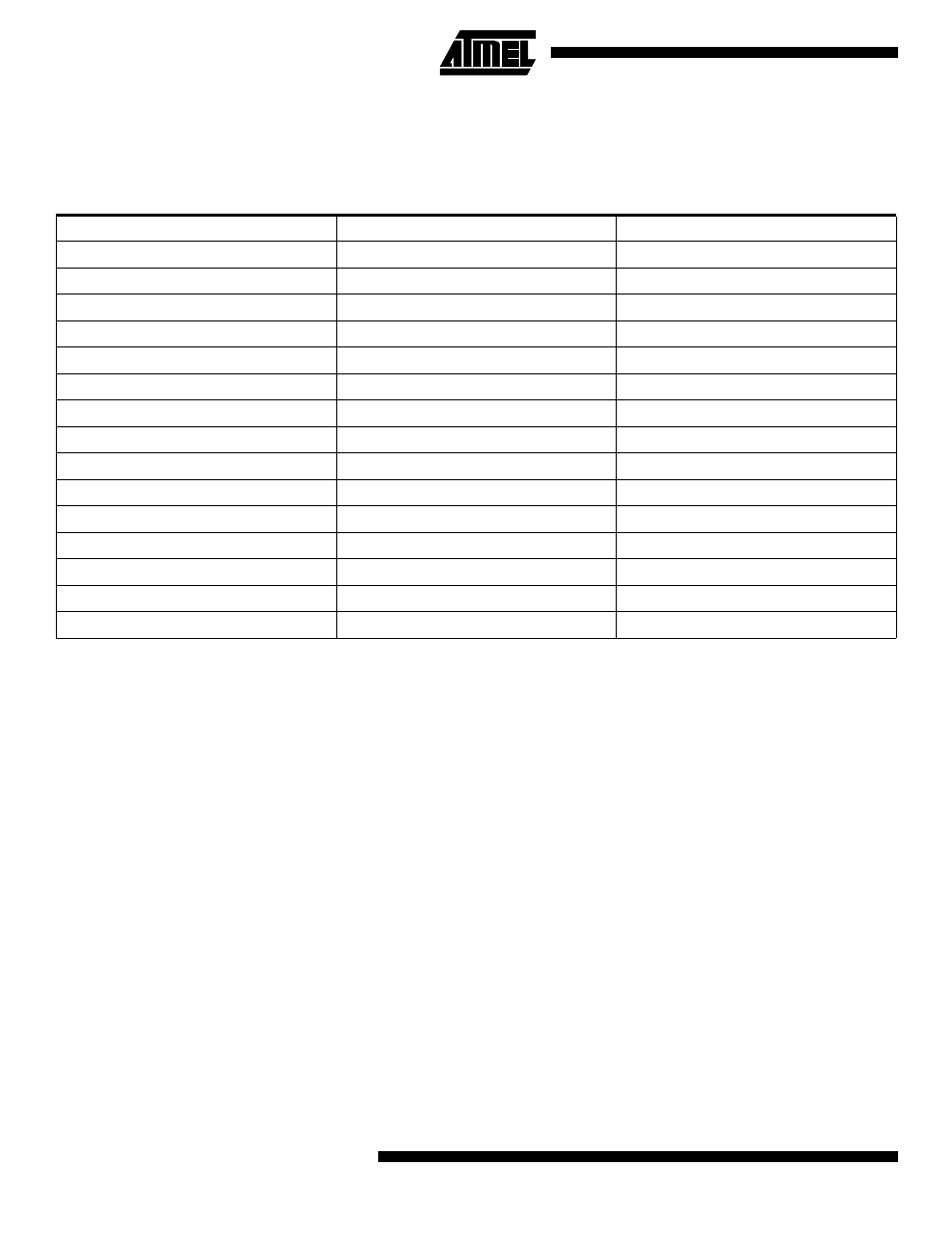

Peripheral Memory Map

The register maps for each peripheral are described in the corresponding section of this datasheet. The peripheral memory

map has 16K bytes reserved for each peripheral.

Initialization

Reset initializes the user interface registers to their default

states as defined in the peripheral sections of this

datasheet and forces the ARM7TDMI to perform the next

instruction fetch from address zero. Except for the program

counter, the ARM core registers do not have defined reset

states. When reset is active, the inputs of the AT75C220

must be held at valid logic levels.

There are three ways in which the AT75C220 can enter

reset:

1.

Hardware reset. Caused by asserting the RESET

pin, e.g., at power-up.

2.

Watchdog timer reset. The WD timer can be pro-

grammed so that if timed out, a pulse is generated

that forces a chip reset.

3.

Software reset. There are two software resets which

are asserted by writing to bits [11:10] of the SIAP

mode register. SIAP_MD[11] forces a software reset

with RM set low and SIAP_MD[10] forces a reset

with RM set high.

Reset Pin

The reset pin should be asserted for a minimum of 10 clock

cycles. However, if external DRAM is fitted, then reset

should be applied for the time interval specified by the

SDRAM datasheet, typically 200 µs. The OakDSPCores

are only released from reset by the ARM program control.

When reset is released, the pin NDSRA/BOOTN is sam-

pled to determine if the ARM should boot from internal

ROM or from external memory connected to NCS0. The

details of this boot operation are described in the section

“Boot Mode” on page 11.

Processor Synchronization

The ARM and the OakDSPCore processors have their own

PLLs and at power-on each processor has its own indeter-

minate lock period. To guarantee proper synchronization of

inter-processor communication through the mailboxes, a

specific reset sequence should be followed.

Once the ARM core is out of reset, it should set and clear

the reset line of the OakDSPCore three times. This guaran-

tees message synchronization between the ARM and the

OakDSPCore.

Table 3. AT75C220 Peripheral Memory Map

Base Address (Normal Mode)

Peripheral

Description

0xFF000000

MODE

AT75C220 Mode Controller

0xFF004000

SMC

Static Memory Controller

0xFF008000

SDMC

SDRAM Controller

0xFF00C000

PIOA

Programmable I/O

0xFF010000

PIO B

Keypad PIO

0xFF014000

TC

Timer/Counter Channels

0xFF018000

USARTA

USART

0xFF01C000

USARTB

USART

0xFF020000

SPI

Serial Peripheral Interface

0xFF024000

Reserved

0xFF028000

WDT

Watchdog Timer

0xFF030000

AIC

Interrupt Controller

0xFF034000

MACA

MAC Ethernet

0xFF038000

MACB

MAC Ethernet

0xFFFFF000

AIC (alias)

Interrupt Controller