Mac statistics register block – Rainbow Electronics AT75C220 User Manual

Page 50

AT75C220

50

MAC Statistics Register Block

These registers reset to zero on a read and stick at all ones

when they count to their maximum value. They should be

read frequently enough to prevent loss of data.

The statistics register block contains the registers found in

Table 16.

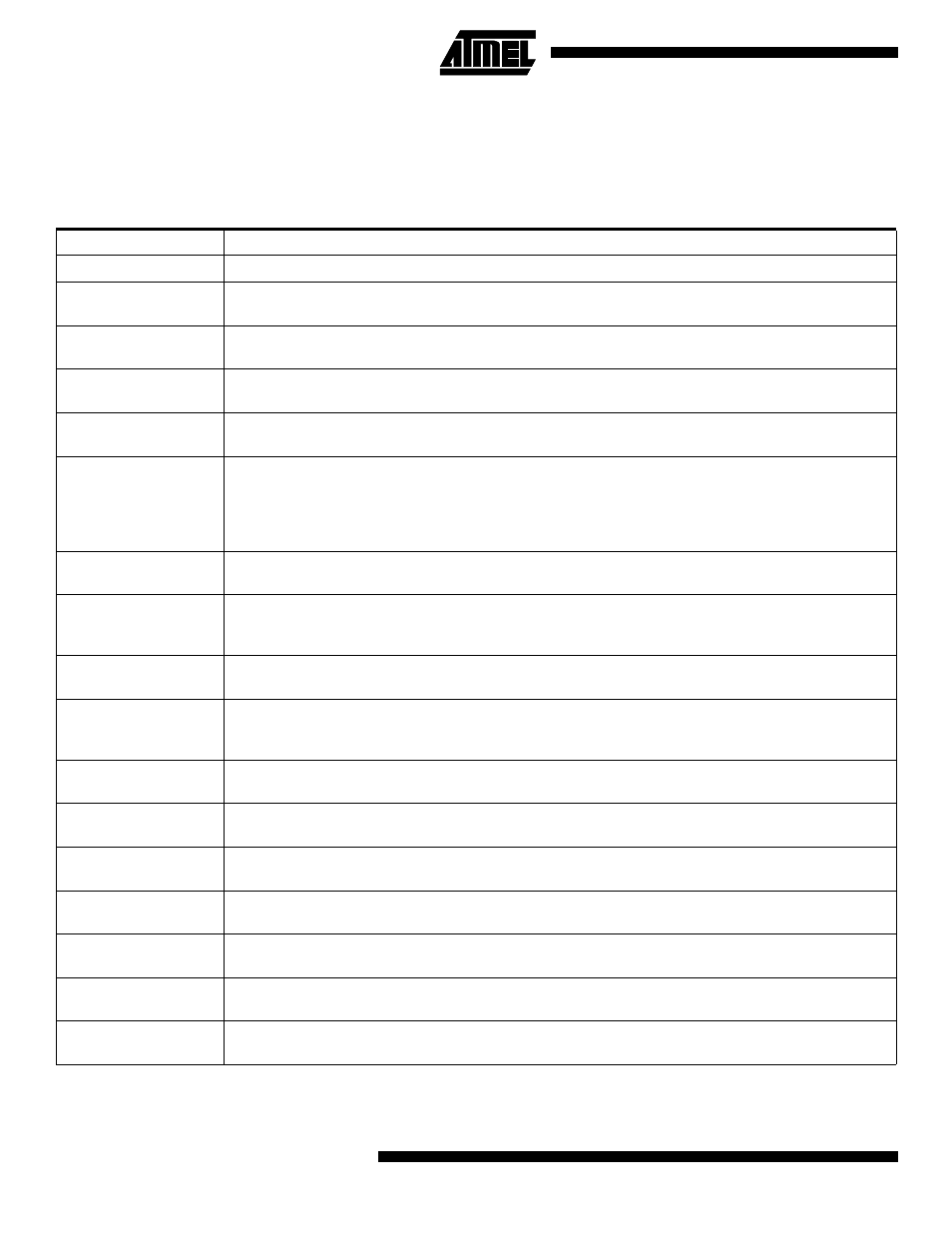

Table 16. Statistics Register Block

Register Name

Description

ETH_FRA

Frames transmitted OK. A 24-bit register counting the number of frames successfully transmitted.

ETH_SCOL

Single collision frames. A 16-bit register counting the number of frames experiencing a single collision

before being transmitted and experiencing no carrier loss nor underrun.

ETH_MCOL

Multiple collision frames. A 16-bit register counting the number of frames experiencing between two and

fifteen collisions prior to being transmitted (62 - 1518 bytes, no carrier loss, no underrun).

ETH_OK

Frames received OK. A 24-bit register counting the number of good frames received, i.e. address

recognized. A good frame is of length 64 to 1518 bytes and has no FCS, alignment or code errors.

ETH_SEQE

Frame checks sequence errors. An 8-bit register counting address-recognized frames with an integral

number of bytes long and that have bad CRC and 64 to 1518 bytes long.

ETH_ALE

Alignment errors. An 8-bit register counting frames that are:

- address recognized,

- not an integral number of bytes long

- have bad CRC when their length is truncated to an integral number of bytes

- between 64 and 1518 bytes in length.

ETH_DTE

Deferred transmission frames. A 16-bit register counting the number of frames experiencing deferral due to

carrier sense active on their first attempt at transmission (no underrun or collision).

ETH_LCOL

Late collisions. An 8-bit register counting the number of frames that experience a collision after the slot

time (512 bits) has expired. No carrier loss or underrun. A late collision is counted twice, i.e., both as a

collision and a late collision.

ETH_ECOL

Excessive collisions. An 8-bit register counting the number of frames that failed to be transmitted because

they experienced 16 collisions. (64 - 1518 bytes, no carrier loss or underrun)

ETH_CSE

Carrier sense errors. An 8-bit register counting the number of frames for which carrier sense was not

detected and maintained in half-duplex mode a slot time (512 bits) after the start of transmission (no

excessive collision).

ETH_TUE

Transmit errors. An 8-bit register counting the number of frames not transmitted due to a transmit DMA

underrun. If this register is incremented, then no other register is incremented.

ETH_CDE

Code errors. An 8-bit register counting the number of frames that are address recognized, had RXER

asserted during reception. If this counter is incremented, then no other counters are incremented.

ETH_ELR

Excessive length frames. An 8-bit register counting the number of frames received exceeding 1518 bytes

in length but that do not have either a CRC error, an alignment error or a code error.

ETH_RJB

Receive jabbers. An 8-bit register counting the number of frames received exceeding 1518 bytes in length

and having either a CRC error, an alignment error or a code error.

ETH_USF

Undersize frames. An 8-bit register counting the number of frames received less than 64 bytes in length

but that do not have either a CRC error, an alignment error or a code error.

ETH_SQEE

SQEE test errors. An 8-bit register counting the number of frames where COL was not asserted within a

slot time of TXEN being deasserted.

ETH_DRFC

Discarded receive frames count. This 16-bit counter is incremented every time an address-recognized

frame is received but cannot be copied to memory because the receive buffer is available.