Clock generation, Peripheral data controller, Spi programmer’s model – Rainbow Electronics AT75C220 User Manual

Page 127: Ee table 27

AT75C220

127

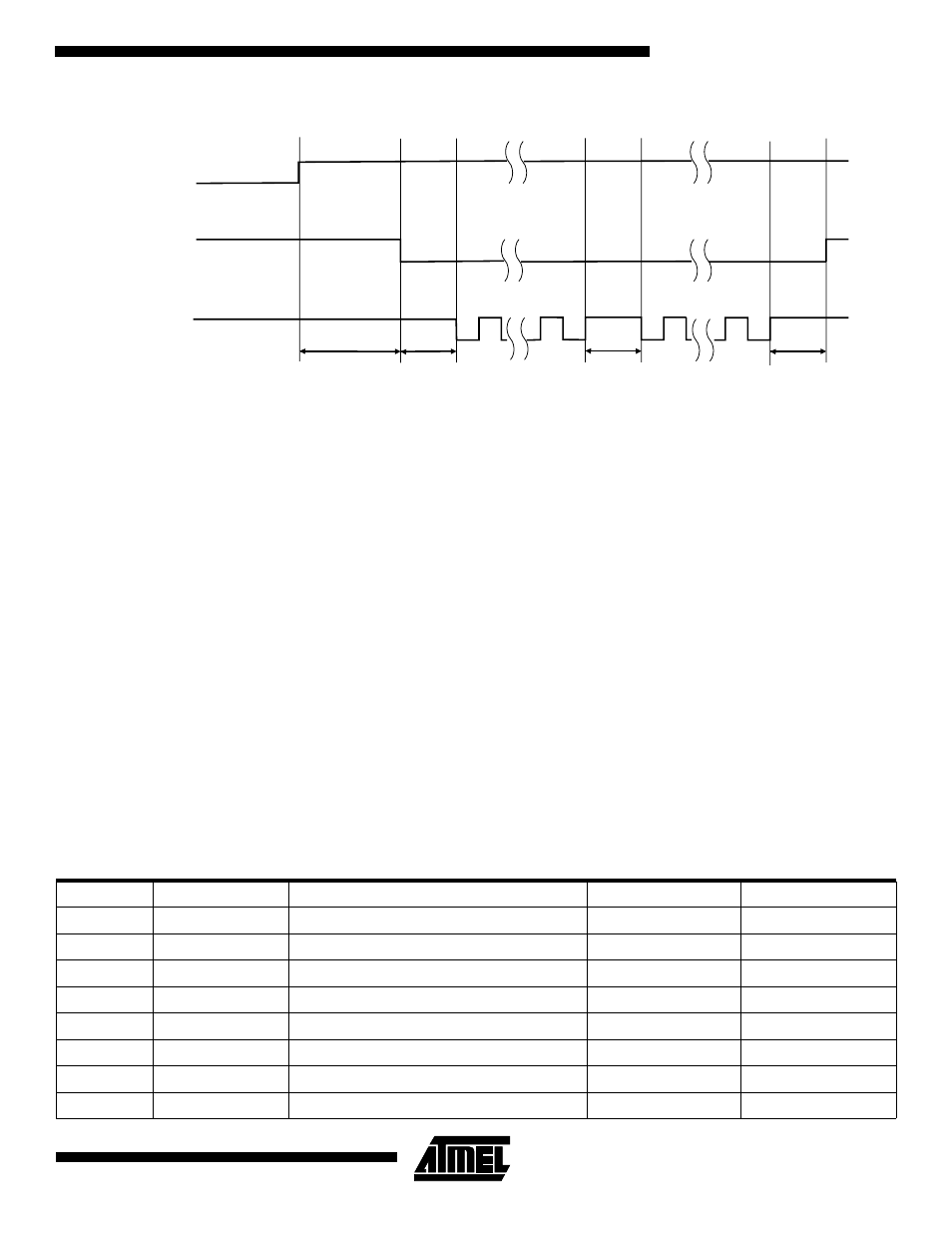

Figure 33. Programmable Delays (DLYBCS, DLYBS and DLTBCT)

Clock Generation

In master mode, the SPI master clock is either ACLK or

ACLK/32, as defined by the MCK32 field of SP_MR. The

SPI baud rate clock is generated by dividing the SPI master

clock by a value between 4 and 510. The divisor is defined

in the SCBR field in each chip select register. The transfer

speed can thus be defined independently for each chip

select signal.

CPOL and NCPHA in the chip select registers define the

clock/data relationship between master and slave devices.

CPOL defines the inactive value of the SPCK. NCPHA

defines which edge causes data to change and which edge

causes data to be captured.

In slave mode, the input clock low and high pulse duration

must strictly be longer than two system clock (ACLK) peri-

ods.

Peripheral Data Controller

The SPI is closely connected to two PDC channels. One is

dedicated to the receiver. The other is dedicated to the

transmitter.

The PDC channel is programmed using SP_TPR and

SP_TCR for the transmitter and SP_RPR and SP_RCR for

the receiver. The status of the PDC is given in SP_SR by

the SPENDTX bit for the transmitter and by the SPENDRX

bit for the receiver.

The pointer registers, SP_TPR and SP_RPR, are used to

store the address of the transmit or receive buffers. The

counter registers, SP_TCR and SP_RCR, are used to store

the size of these buffers.

The receiver data transfer is triggered by the RDRF bit and

the transmitter data transfer is triggered by TDRE. When a

transfer is performed, the counter is decremented and the

pointer is incremented. When the counter reaches 0, the

status bit is set (SPENDRX for the receiver, SPENDTX for

the transmitter in SP_SR) and can be programmed to gen-

erate an interrupt. While the counter is at zero, the status

bit is asserted and transfers are disabled

SPI Programmer’s Model

SPI Base Address: 0xFF020000.

Chip Select 1

Chip Select 2

SPCK Output

DLYBCS

DLYBS

DLYBCT

Change peripheral

No change

of peripheral

DLYBCT

Table 27. SPI Memory Map

Offset

Register Name

Register

Access

Reset Value

0x00

SP_CR

Control Register

Write-only

–

0x04

SP_MR

Mode Register

Read/write

0

0x08

SP_RDR

Receive Data Register

Read-only

0

0x0C

SP_TDR

Transmit Data Register

Write-only

–

0x10

SP_SR

Status Register

Read-only

0

0x14

SP_IER

Interrupt Enable Register

Write-only

–

0x18

SP_IDR

Interrupt Disable Register

Write-only

–

0x1C

SP_IMR

Interrupt Mask Register

Read-only

0