Ethernet mac, Dma operation, Transmitter mode – Rainbow Electronics AT75C220 User Manual

Page 33

AT75C220

33

Ethernet MAC

The AT75C220 integrates two identical Ethernet MACs,

known as MAC A and MAC B.

The Ethernet MAC is described more fully in the IEEE stan-

dard 802.3. It is a programmable device on the APB bus by

means of 56 configuration and status registers. The Ether-

net MAC is an ASB master.

The main features of the Ethernet MAC are:

• Compatibility with IEEE standard 802.3

• 10 and 100 Mbit/s operation

• Full-and half-duplex operation

• MII interface to the physical layer

• Register interface to address, status and control

registers

• DMA interface

• Interrupt generation to signal receive and transmit

completion

• 28-byte transmit and 28-byte receive FIFOs

• Automatic pad and CRC generation on transmitted

frames

• Address checking logic to recognize four 48-bit

addresses

• Supports promiscuous mode where all valid frames are

copied to memory

• Supports physical layer management through MDIO

interface

DMA Operation

Frame data is transferred to and from the Ethernet MAC via

the DMA interface. All transfers are 32-bit words and may

be single accesses or bursts of two, three or four words.

Burst accesses do not cross 16-byte boundaries.

The DMA controller performs four types of operations on

the ASB bus. In order of priority, they are receive buffer

manager write, receive buffer manager read, transmit data

DMA read and receive data DMA write.

Transmitter Mode

Transmit frame data needs to be stored in contiguous

memory locations and need not be word-aligned.

The transmit address register is written with the address of

the first byte to be transmitted. Transmit is initiated by writ-

ing the number of bytes to transfer (length) to the transmit

control register. The transmit channel then reads data from

memory 32 bits at a time and places them in the transmit

FIFO.

The transmit block starts frame transmission once three

words have been loaded into the FIFO.

The transmit address register must be written before the

transmit control register. While a frame is being transmit-

ted, it is possible to set up one other frame for transmission

by writing new values to the transmit address and control

registers. Reading the transmit address register returns the

address of the buffer currently being accessed by the trans-

mit FIFO. Reading the transmit control register returns the

total number of bytes to be transmitted. The buffer not

queued bit in the transmit status register indicates whether

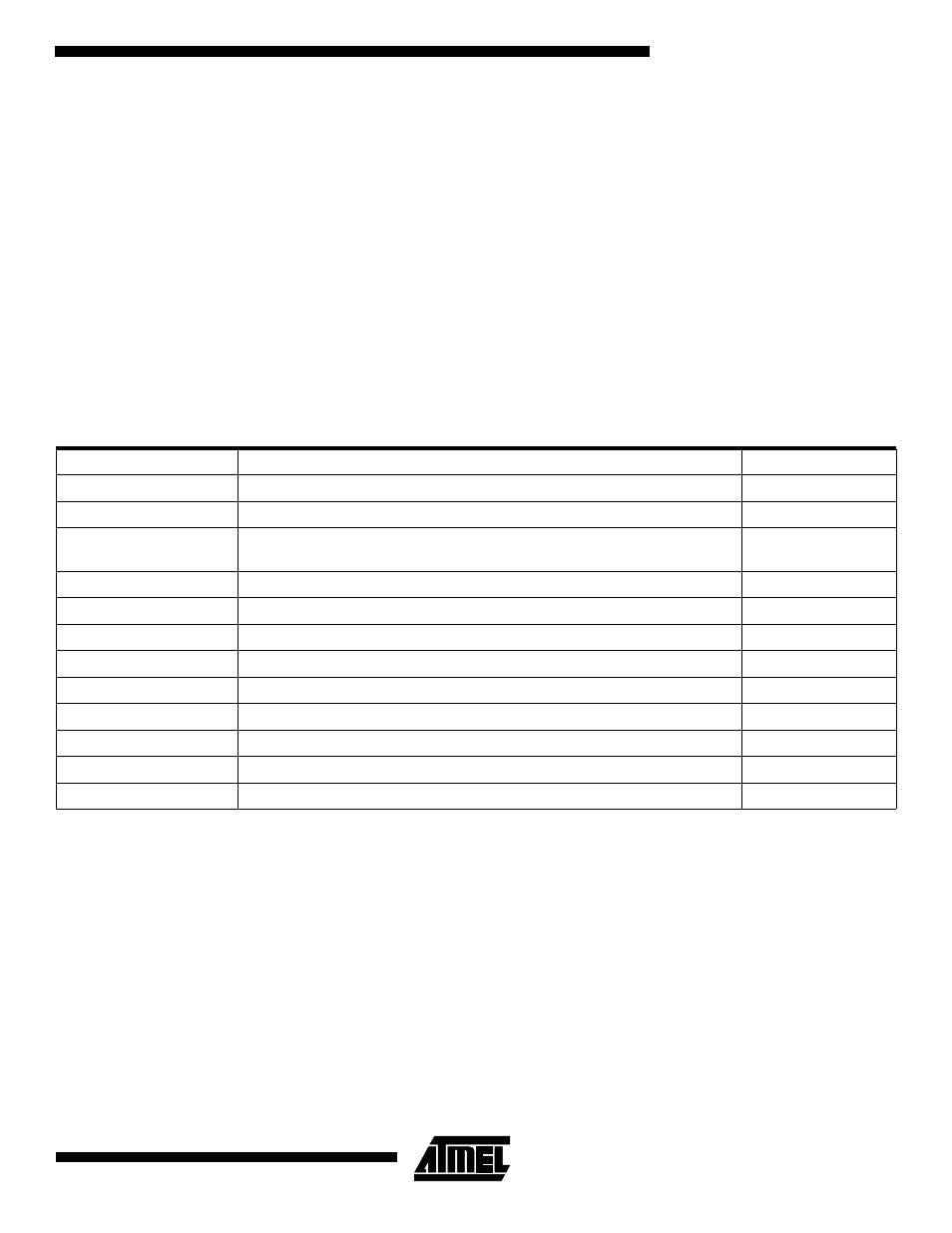

Table 13. External Interface

Signal Name

Description

Type

COL

Collision detect from the PHY

Input

CRS

Carrier sense from the PHY

Input

TXER

Transmit error signal to the PHY. Asserted if the DMA block fails to fetch data

from memory during frame transmission.

Output

TXD[3:0]

Transmit data to the PHY

Output

TXEN

Transmit enable to the PHY

Output

TXCLK

Transmit clock from the PHY

Input

RXD[3:0]

Receive data from the PHY

Input

RXER

Receive error signal from the PHY

Input

RXCLK

Receive clock from the PHY

Input

RXDV

Receive data valid signal from the PHY

Input

MDC

Management data clock

Output

MDIO

Management data I/O

Input/Output