Rf22, Controller interface, Serial peripheral interface (spi) – Rainbow Electronics RF22 User Manual

Page 8: Figure2. tx timing. figure3. rx timing, Figure4. spi timing, Table10. serial interface timing parameters, Sdi nsel sclk, Symbol parameter min (nsec) diagram t, Clock high time 40 t, Clock low time 40 t

RF22

Version: 0.1 Date: 12/23/2008

Tel: +86-755-82973805 Fax: +86-755-82973550 E-mail: [email protected] http://www.hoperf.com

8

TX Packet

XTAL Settling

Time

0T

L

L

P

L

A

C

LL

P

S

T

L

L

P

~1ms

P

M

A

R

A

P

E

R

P

P

U

P

M

A

R

A

P

Y

A

L

E

D

D

O

M

X

T

N

W

O

D

P

M

A

R

A

P

C

onf

ig

ur

abl

e 0~

70u

s, D

ef

aul

t=20u

s

45

us,

may be sk

ipe

d

C

onf

igur

ab

le

0~

31

0us,

Rec

ommen

ded 10

0us

6

us,

F

ixe

d

C

onf

ig

ur

abl

e 5~

20u

s, R

eco

mmende

d

5

us

1.5

B

it

s@D

R

RX Packet

XTAL Settling

Time

0T

LL

P

L

A

C

L

L

P

ST

L

L

P

~1ms

C

onfigur

able 0~70

us,

Default=20

us

45

us, ma

y be sk

ip

ed

Con

figura

ble 0

~

310u

s, Rec

ommended 100us

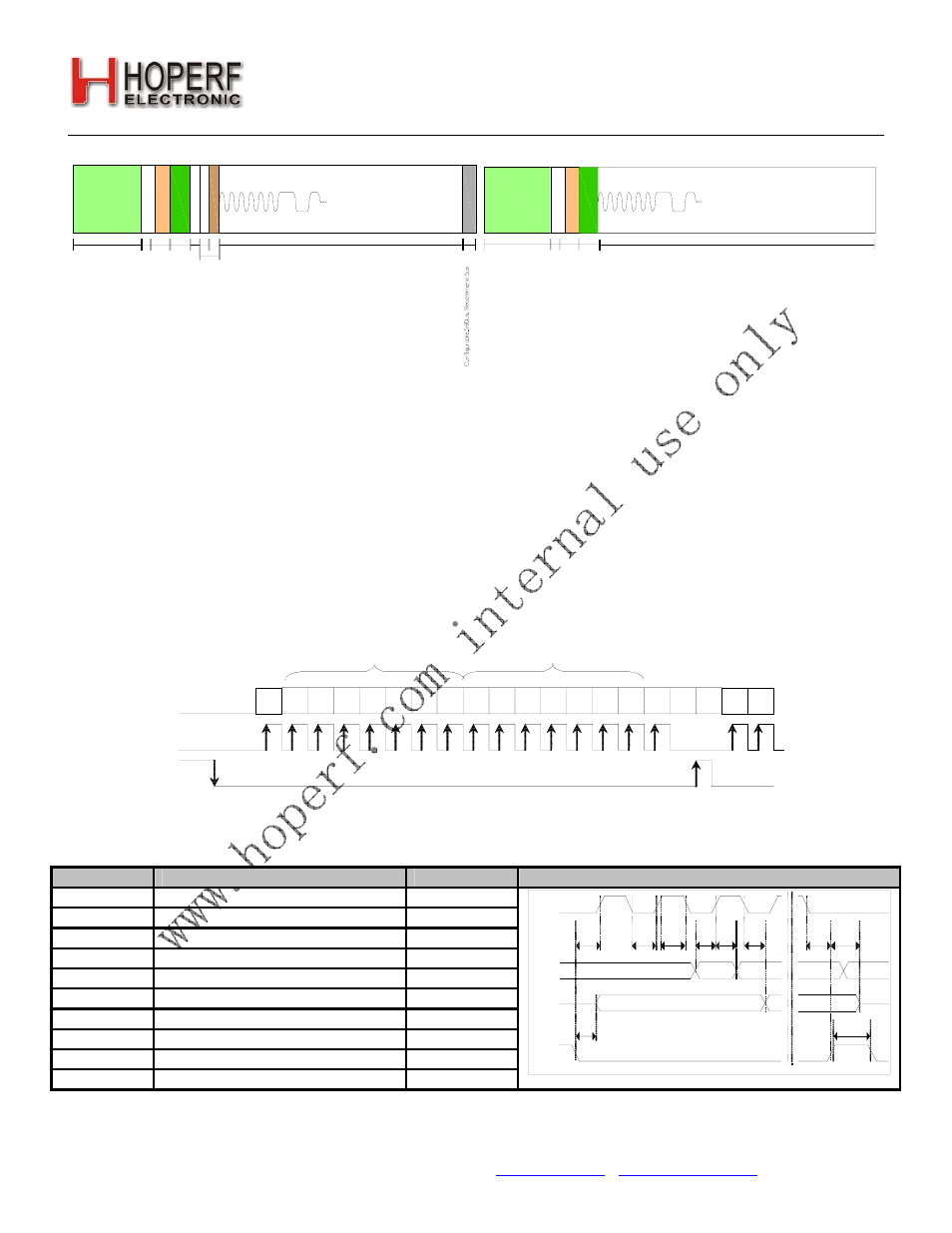

Figure2. TX Timing. Figure3. RX Timing

3. Controller Interface

3.1. Serial Peripheral Interface (SPI)

The RF22 communicates with the host MCU over a 3 wire SPI interface: SCLK, SDI, and nSEL. The host MCU can

also read data from internal registers on the SDO output pin. A SPI transaction is a 16-bit sequence which consists of a

Read-Write (R/W) select bit, followed by a 7-bit address field (ADDR), and an 8-bit data field (DATA), as demonstrated

in Figure 4. The 7-bit address field supports reading from or writing to one of the 128, 8-bit control registers. The R/W

select bit determines whether the SPI transaction is a write or read transaction. If R/W = 1, it signifies a WRITE

transaction, while R/W = 0 signifies a READ transaction. The contents (ADDR or DATA) are latched into the RF22

every eight clock cycles. The timing parameters for the SPI interface are shown in Table 10. The SCLK rate is flexible

with a maximum rate of 10 MHz.

Address

Data

RW

A5

A3

RW A7

A6

xx

xx

A4

D0

A2 A1 A0 D7 D6 D5 D4 D3 D2 D1

LSB

MSB

SDI

nSEL

SCLK

Figure4. SPI Timing

Table10. Serial Interface Timing Parameters

Symbol

Parameter

Min (nsec)

Diagram

t

CH

Clock high time

40

t

CL

Clock low time

40

t

DS

Data setup time

20

t

DH

Data hold time

20

t

DD

Output data delay time

20

t

EN

Output enable time

20

t

DE

Output disable time

50

t

SS

Select setup time

20

t

SH

Select hold time

50

t

SW

Select high period

80

SW

t

DE

t

SH

t

N

E

t

SS

t

DD

t

DH

t

DS

t

CH

t

CL

t

nSEL

SCLK

SDI

SDO