Rf22 – Rainbow Electronics RF22 User Manual

Page 54

RF22

Version: 0.1 Date: 12/23/2008

Tel: +86-755-82973805 Fax: +86-755-82973550 E-mail: [email protected] http://www.hoperf.com

54

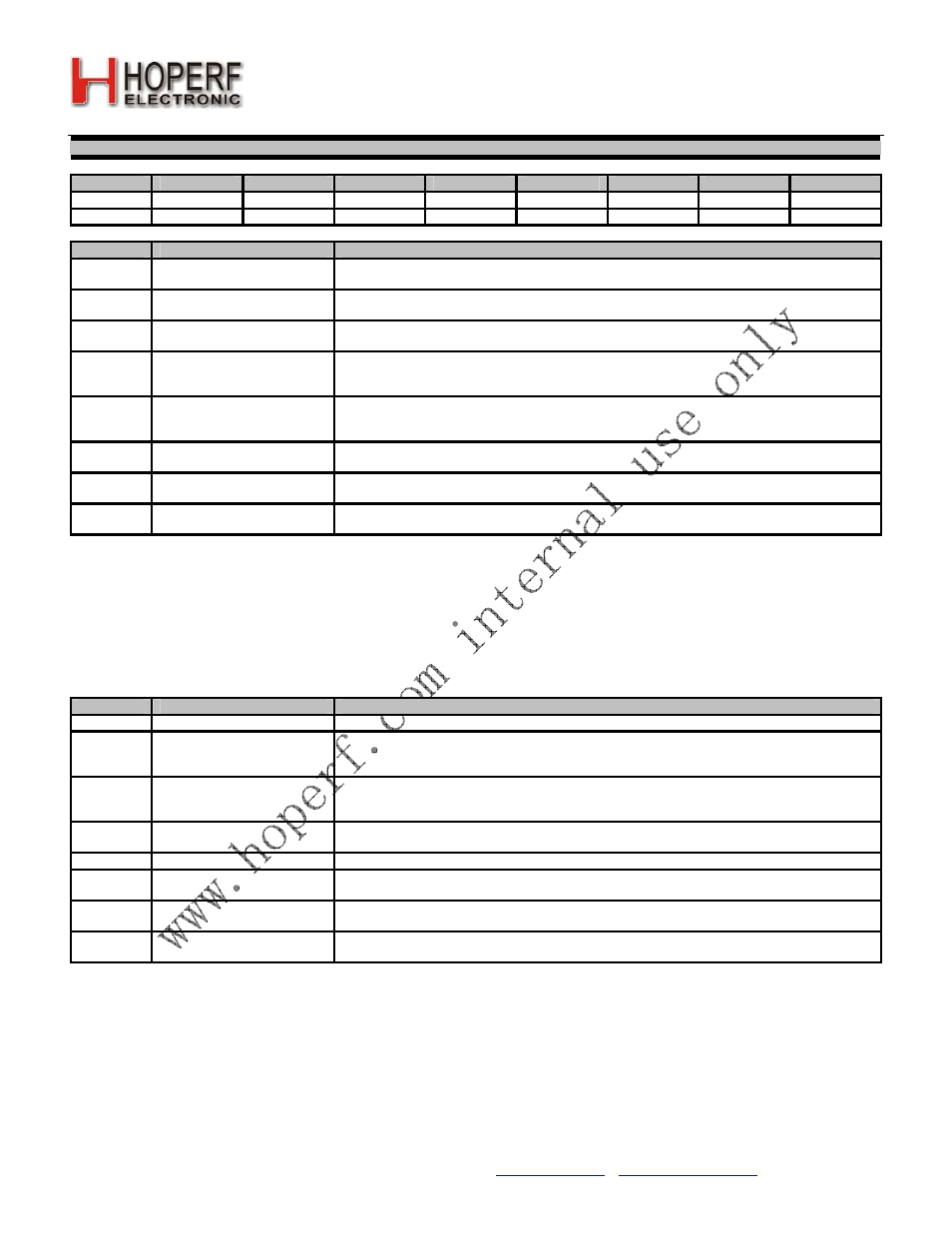

Register 03h. Interrupt/Status 1

Bit

D7

D6

D5

D4

D3

D2

D1

D0

Name

ifferr

itxffafull

itxffaem

irxffafull

iext

ipksent

ipkvalid

icrcerror

Type

R

R

R

R

R

R

R

R

Reset value = xxxxxxxx

Bit

Name

Function

7

ifferr

FIFO Underflow/Overflow Error.

When set to 1 the TX or RX FIFO has overflowed or underflowed.

6

itxffafull

TX FIFO Almost Full.

When set to 1 the TX FIFO has met its almost full threshold and needs to be transmitted.

5

itxffaem

TX FIFO Almost Empty.

When set to 1 the TX FIFO is almost empty and needs to be filled.

4

irxffafull

RX FIFO Almost Full.

When set to 1 the RX FIFO has met its almost full threshold and needs to be read by the

microcontroller.

3

iext

External Interrupt.

When set to 1 an interrupt occurred on one of the GPIO’s if it is programmed so. The status can

be checked in register 0Eh. See GPIOx Configuration section for the details.

2

ipksent

Packet Sent Interrupt.

When set to1 a valid packet has been transmitted.

1

ipkvalid

Valid Packet Received.

When set to 1 a valid packet has been received.

0

icrcerror

CRC Error.

When set to 1 the cyclic redundancy check is failed.

When any of the Interrupt/Status 1 bits change state from 0 to 1 the device will notify the microcontroller by setting the

nIRQ pin LOW if it is enabled in the Interrupt Enable 1 register. The nIRQ pin will go to HIGH and all the enabled

interrupt bits will be cleared when the microcontroller reads this address. If any of these bits is not enabled in the

Interrupt Enable 1 register then it becomes a status signal that can be read anytime in the same location and will not be

cleared by reading the register.

Table 33. Interrupt or Status 1 Bit Set/Clear Description

Bit

Status Name

Set/Clear Conditions

7

ifferr

Set if there is a TX or RX FIFO overflow or underflow. Cleared by applying FIFO reset.

6

itxffafull

Set when the number of bytes written to TX FIFO is greater than the Almost Full threshold.

Automatically cleared at the start of transmission when the number of bytes in the FIFO is less

than or equal to the threshold.

5

itxffaem

Set when the number of bytes in the TX FIFO is less than or equal to the Almost Empty

threshold. Automatically cleared when the number of data bytes in the TX FIFO is above the

Almost Empty threshold.

4

irxffafull

Set when the number of bytes in the RX FIFO is greater than the Almost Full threshold. Cleared

when the number of bytes in the RX FIFO is below the Almost Full threshold.

3

iext

External interrupt source.

2

ipksent

Set once a packet is successfully sent (no TX abort). Cleared upon leaving FIFO mode or at the

start of a new transmission.

1

ipkvalid

Set up the successful reception of a packet (no RX abort). Cleared upon receiving and

acknowledging the Sync Word for the next packet.

0

icrcerror

Set if the CRC computed from the RX packet differs from the CRC in the TX packet. Cleared at

the start of reception for the next packet.