Rf22 – Rainbow Electronics RF22 User Manual

Page 58

RF22

Version: 0.1 Date: 12/23/2008

Tel: +86-755-82973805 Fax: +86-755-82973550 E-mail: [email protected] http://www.hoperf.com

58

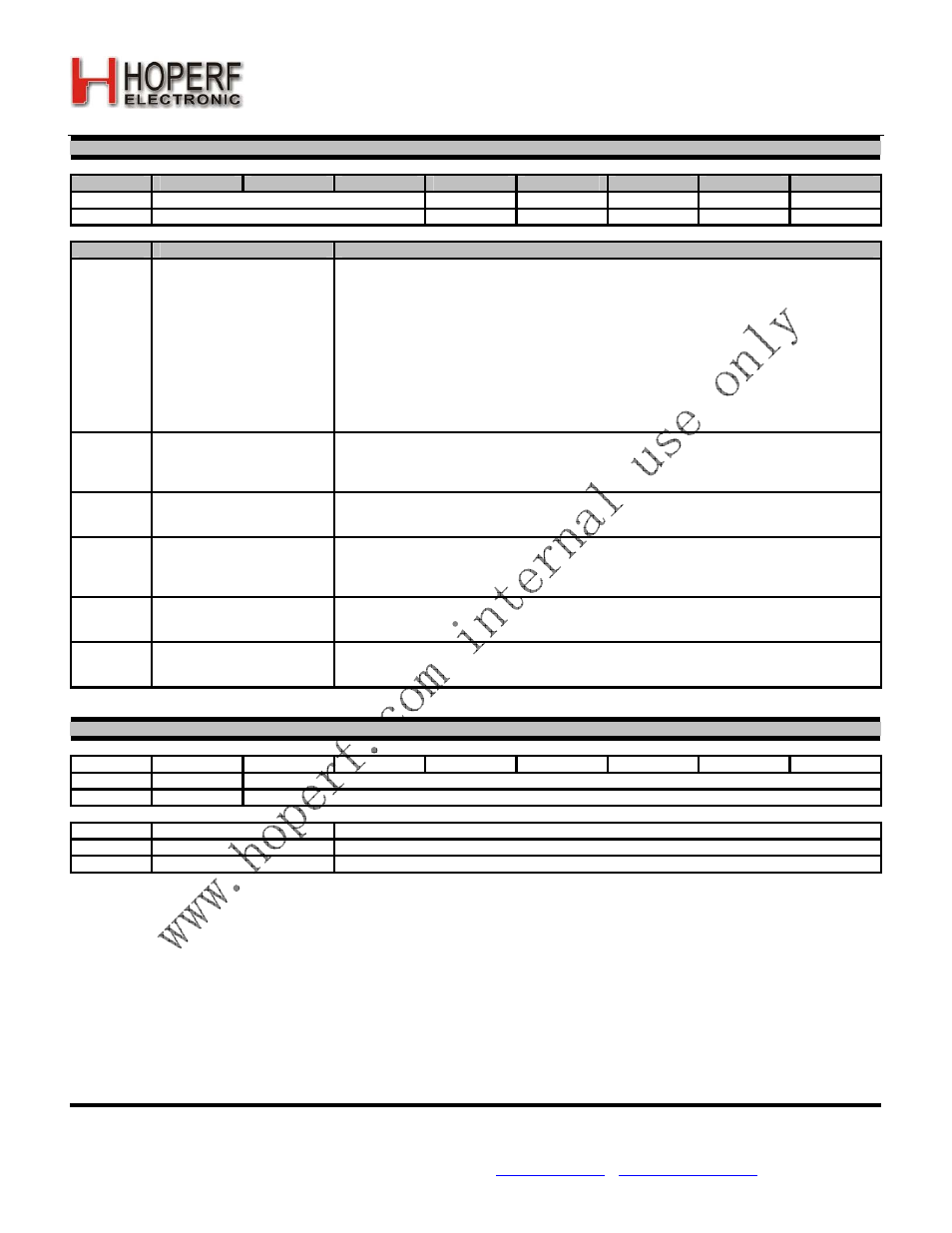

Register 08h. Operating Mode and Function Control 2

Bit

D7

D6

D5

D4

D3

D2

D1

D0

Name

antdiv[2:0]

rxmpk

autotx

enldm

ffclrrx

ffclrtx

Type

R/W

R/W

R/W

R/W

R/W

R/W

Reset value = 00000000

Bit

Name

Function

7:5

antdiv[2:0]

Enable Antenna Diversity.

The GPIO must be configured for Antenna Diversity for the algorithm to work properly.

RX/TX state non RX/TX state

GPIO Ant1 GPIO Ant2 GPIO Ant1 GPIO Ant2

000: 1 0 0 0

001: 0 1 0 0

010: 1 0 1 1

011: 0 1 1 1

100: antenna diversity algorithm 0 0

101: antenna diversity algorithm 1 1

110: ant. div. algorithm in beacon mode 0 0

111: ant. div. algorithm in beacon mode 1 1

4

rxmpk

RX Multi Packet.

When the chip is selected to use FIFO Mode (dtmod[1:0]) and RX Packet Handling (enpacrx)

then it will fill up the FIFO with multiple valid packets if this bit is set, otherwise the transceiver will

automatically leave the RX State after the first valid packet has been received.

3

autotx

Automatic Transmission.

When autotx = 1 the transceiver will enter automatically TX State when the FIFO is almost full.

When the FIFO is empty it will automatically return to the Idle State.

2

enldm

Enable Low Duty Cycle Mode.

If this bit is set to 1 then the chip turns on the RX regularly. The frequency should be set in the

Wake-Up Timer Period register, while the minimum ON time should be set in the Low-Duty Cycle

Mode Duration register. The FIFO mode should be enabled also.

1

ffclrrx

RX FIFO Reset/Clear.

This has to be a two writes operation: Setting ffclrrx=1 followed by ffclrrx= 0 will clear the

contents of the RX FIFO.

0

ffclrtx

TX FIFO Reset/Clear.

This has to be a two writes operation: Setting ffclrtx=1 followed by ffclrtx= 0 will clear the contents

of the TX FIFO.

Register 09h. 30 MHz Crystal Oscillator Load Capacitance

Bit

D7

D6

D5

D4

D3

D2

D1

D0

Name

xtalshft

xlc[6:0]

Type

R/W

R/W

Reset value = 01000000

Bit

Name

Function

7

xtalshft

Direct Control to Analog.

6:0

xlc[6:0]

Tuning Capacitance for the 30 MHz XTAL.