Rf22 – Rainbow Electronics RF22 User Manual

Page 79

RF22

Version: 0.1 Date: 12/23/2008

Tel: +86-755-82973805 Fax: +86-755-82973550 E-mail: [email protected] http://www.hoperf.com

79

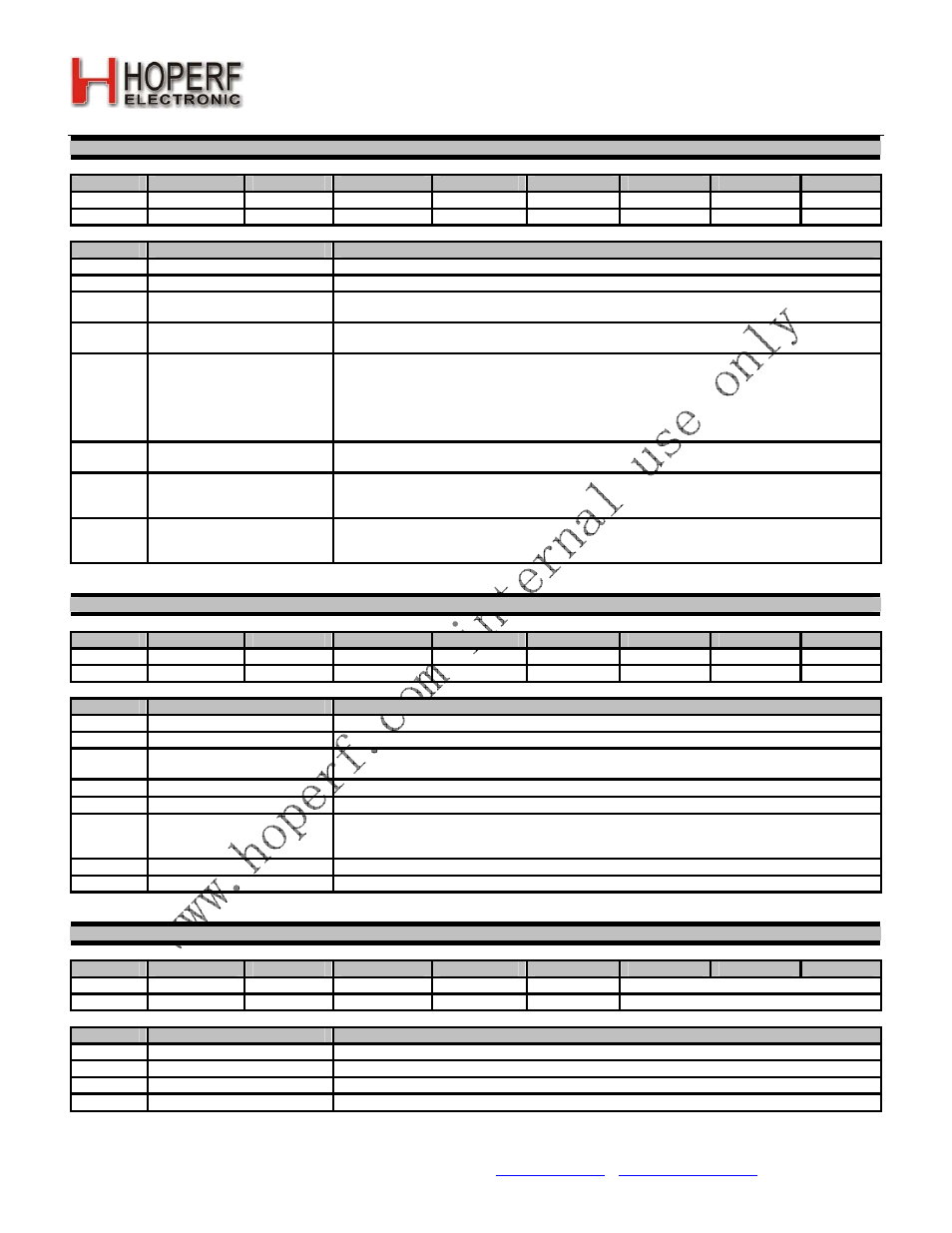

Register 55h. Calibration Control

Bit

D7

D6

D5

D4

D3

D2

D1

D0

Name

Reserved

xtalstarthalf

adccaldone

enrcfcal

rocal

vcocaldp

vcocal

skipvco

Type

R

R/W

R

R/W

R/W

R/W

R/W

R/W

Reset value = x0x00100

Bit

Name

Function

7

Reserved

Reserved.

6

xtalstarthalf

If Set, the Xtal Wake Time Period is Halved.

5

adccaldone

Delta-sigma ADC Calibration Done.

Reading this bit gives 1 if the calibration process has been finished.

4

enrcfcal

RC Oscillator Fine Calibration Enable.

If this bit is set to 1 then the RC oscillator performs fine calibration in every app. 30 s.

3

rccal

RC Calibration Force.

If setting rccal = 1 will automatically perform a forced calibration of the 32 kHz RC Oscillator. The

RC OSC will automatically be calibrated if the Wake-Up-Timer is enabled or if in the

Wake-on-Receiver state. The calibration takes 2 ms. The 32 kHz RC oscillator must be enabled

to perform a calibration. Setting this signal from a 0 to 1 will initiate the calibration. This bit is

cleared automatically.

2

vcocaldp

VCO Calibration Double Precision Enable.

When this bit is set to 1 then the VCO calibration measures longer thus calibrates more precisely.

1

vcocal

VCO Calibration Force.

If in Idle Mode and pllon = 1, setting vcocal = 1 will force a one time calibration of the synthesizer

VCO. This bit is cleared automatically.

0

skipvco

Skip VCO Calibration.

Setting skipvco = 1 will skip the VCO calibration when going from the Idle state to the TX or RX

state.

Register 56h. Modem Test

Bit

D7

D6

D5

D4

D3

D2

D1

D0

Name

bcrfbyp

slicfbyp

dttype

afcpol

spare

refclksel

refclkinv

iqswitch

Type

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Reset value = 00000000

Bit

Name

Function

7

bcrfbyp

If set, BCR phase compensation will be bypassed.

6

slicfbyp

If set, slicer phase compensation will be bypassed.

5

dttype

Dithering Type.

If low and dither enabled, we add +1/0, otherwise if high and dithering enabled, we add +1/–1.

4

afcpol

AFC loop polarity selector (costumer should not touch it).

3

spare

Spare Bit.

2

refclksel

Delta-Sigma Reference Clock Source Selection

1: 10 MHz

0: PLL

1

refclkinv

Delta-Sigma Reference Clock Inversion Enable.

0

iqswitch

I&Q Channel Switch Enable.

Register 57h. Charge Pump Test

Bit

D7

D6

D5

D4

D3

D2

D1

D0

Name

pfdrst

fbdiv_rst

cpforceup

cpforcedn

cdonly

cdcurr[2:0]

Type

R/W

R/W

R/W

R/W

R/W

R/W

Reset value = 00000000

Bit

Name

Function

7

pfdrst

Direct Control to Analog.

6

fbdiv_rst

Direct Control to Analog.

5

cpforceup

Charge Pump Force Up.

4

cpforcedn

Charge Pump Force Down.