7 configuration and initialization – Intel SE7525GP2 User Manual

Page 58

Intel® Server Board SE7320SP2 & Intel Server Board SE7525GP2 TPS

Functional Architecture

Revision 2.0

58

3.7 Configuration and Initialization

This section describes the initial programming environment including address maps for memory

and I/O, techniques and considerations for programming ASIC registers, and hardware options

configuration.

3.7.1 Memory

Space

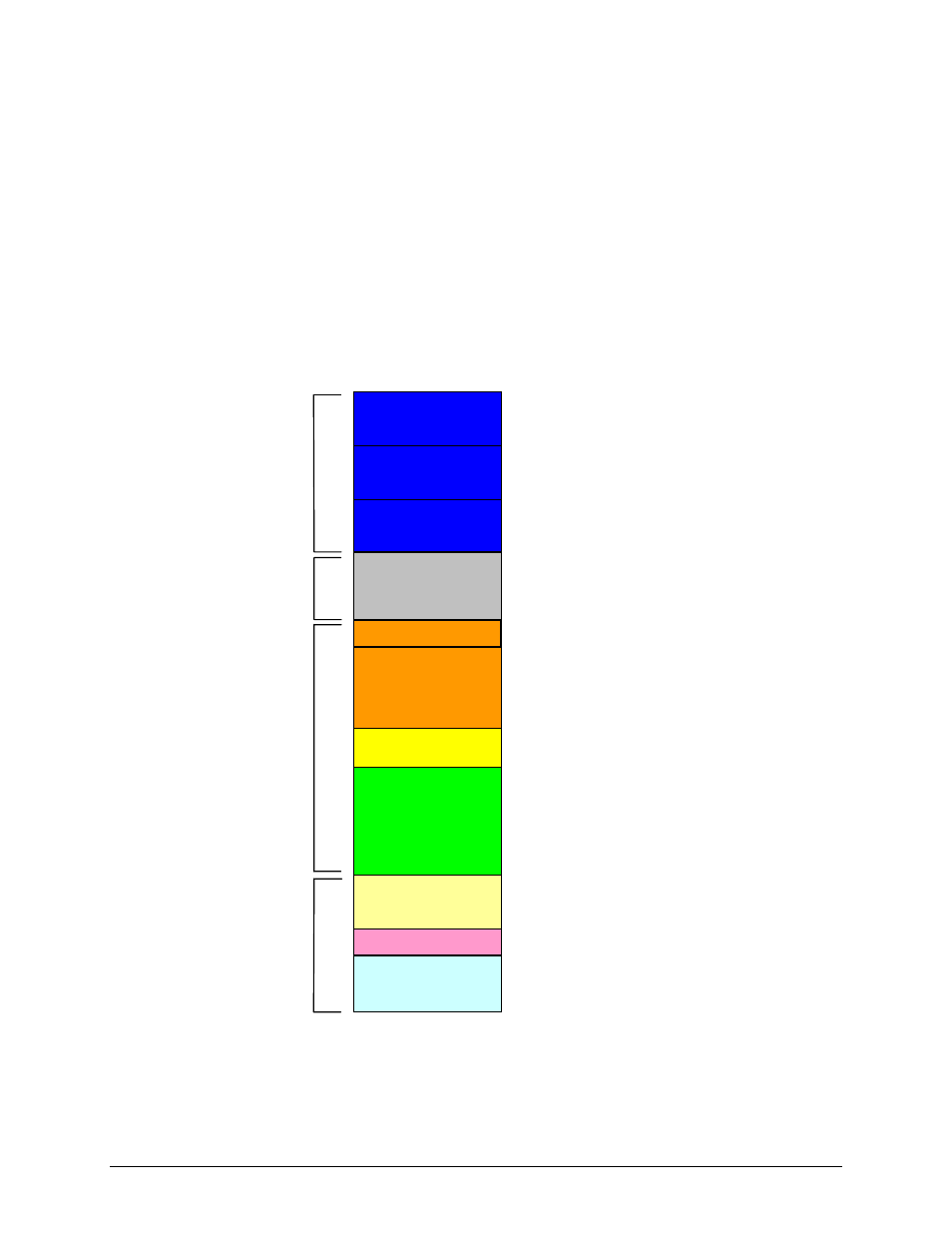

At the highest level, the Intel Xeon processor address space is divided into 4 regions, as shown

in the following figure. Each region contains sub-regions as described in following sections.

Attributes can be independently assigned to regions and sub-regions using the Intel Server

Board SE7320SP2 or SE7525GP2 registers. The Intel E7320 and Intel E7525 chipsets each

supports 64GB of host-addressable memory space and 64KB+3 of host-addressable I/O space.

The SE7320SP2 and server board SE7525GP2s support up to 8GB of main memory for DDR-

266 or DDR-333 configurations.

Figure 9 - Intel® Xeon™ Processor Memory address Space

4GB

Optional ISA Hole

Top of Low Memory (TOLM)

16MB

15MB

1MB

640KB

512KB

0

Additional Main

Memory Address

Main Memory

Address Range

DOS Legacy

Address Range

Lo PCI

Memory Space

Range

TSEG SMRAM

64GB

Hi PCI

Memory

Upper Memory

Ranges