Intel SE7525GP2 User Manual

Page 109

Intel® Server Board SE7320SP2 & Intel Server Board SE7525GP2 TPS

Platform Management

Revision 2.0

109

5.2.3 SMBus

Interfaces

The mBMC incorporates one slave and two master-only SMBus interfaces. The mBMC

interfaces with the host through the slave SMBus interface. It interfaces with the LAN On

Motherboard (LOM) and peripherals through the two independent master bus interfaces.

5.2.4

External Interface to mBMC

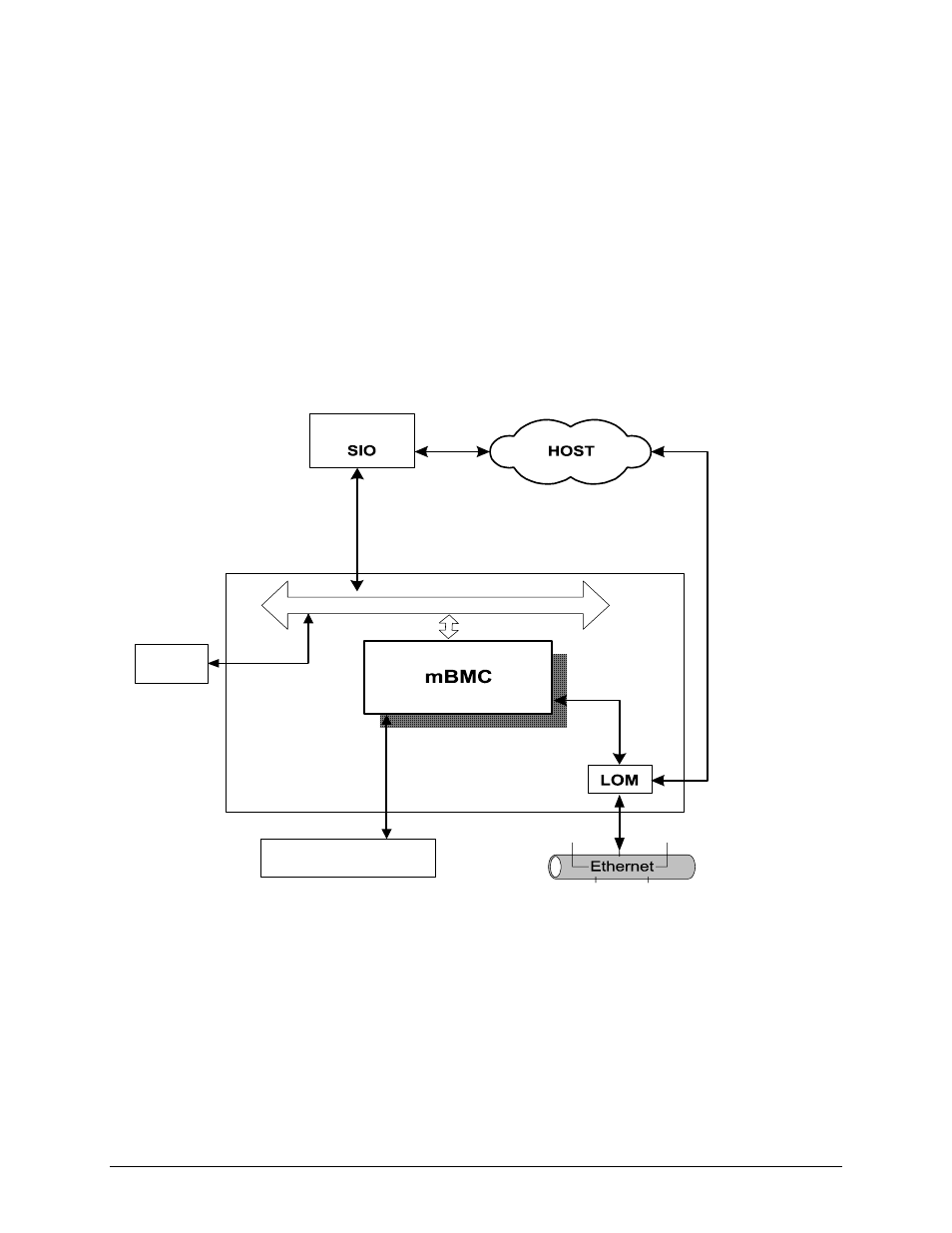

Figure 15 shows the data/control flow to and within the functional modules of the mBMC.

External interfaces from the host system, LOM, and peripherals, interact with the mBMC

through the corresponding interface modules as shown.

The mBMC communicates with the internal modules using its private SMBus. External devices

and sensors interact with the mBMC using the peripheral SMBus. LOM communicates through

the LOM SMBus. GPIO pins are available and are used for various Input and Output functions.

Dedicated LED lines are used for LED/color control.

Also built into the mBMC are the control functions for both the power supply and front panel.

Figure 15: External Interfaces to mBMC

5.2.4.1

Private Management I

2

C Buses

The mBMC implements a single private management bus. The mBMC is the sole master on this

bus. External agents must use the mBMC Master Write/Read I

2

C command if they require direct

communication with a device on this bus. In addition, the mBMC provides a Reserve Device

command that gives an external agent exclusive access to a specific device for a selectable

time.

P C I

S M B u s

S M B u s

S e n so r

D ev ice s

F ro nt P an el