Parallel port – Intel CHIPSET 820E User Manual

Page 225

3-20-2000_10:15

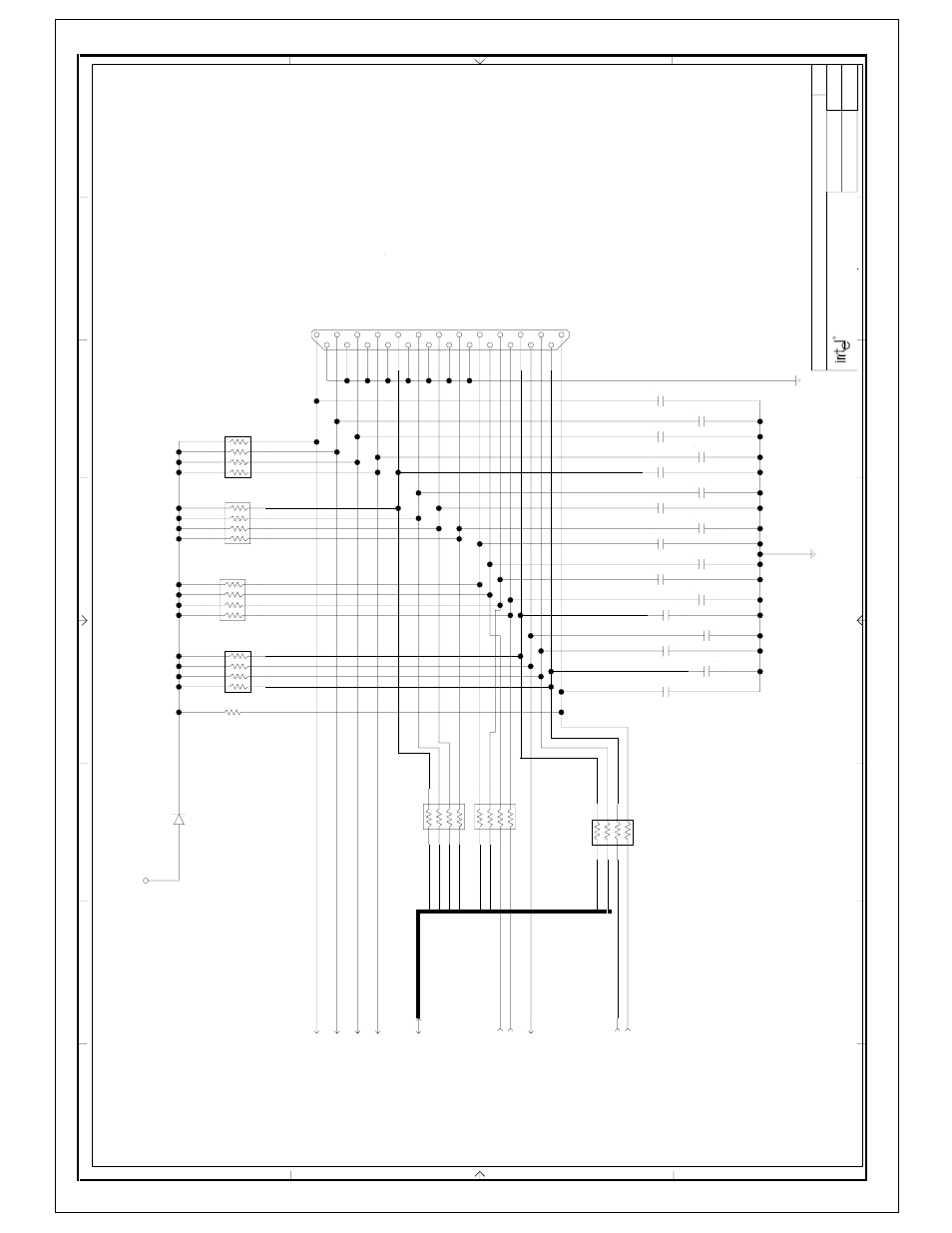

PARALLEL PORT

29

PDR7_R

PDR6_R

PDR5_R

PDR4_R

PDR3_R

SLIN#_R

PDR2_R

PAR_INIT#_R

VCC5_DB25_CR

SLCT

12

PE

12

BUSY

12

ACK#

12

SLIN#

12

J6

P15

P16

P13

P23

P10

P25

P12

P24

P11

P22

P9

P21

P8

P20

P7

P19

P6

P18

P5

P17

P4

P3

P2

P14

P1

12

STB#

2.2K

R40

33

RP18

1

2

3

45

6

7

8

33

RP19

8

7

6

5

4

3

2

1

12

PAR_INIT#

12

ERR#

PDR0_R

STB#_R

180PF

C81

180PF

CP2

6

3

180PF

CP2

4

5

180PF

CP2

1

8

180PF

CP2

7

2

RP20

33

1

2

3

4

5

6

7

8

12

AFD#

PDR0

PDR1

12

PDR[7:0]

PDR4

PDR5

PDR6

PDR7

PDR3

PDR2

180PF

CP5

5

4

180PF

CP5

3

6

180PF

CP5

7

2

180PF

CP5

1

8

RP4

2.2K

1

2

3

4

5

6

7

8

PDR1_R

RP1

2.2K

8

7

6

5

4

3

2

1

AFD#_R

180PF

CP3

1

8

180PF

CP3

7

2

CP3

180PF

6

3

180PF

CP3

4

5

RP2

2.2K

1

2

3

4

5

6

7

8

RP3

2.2K

8

7

6

5

4

3

2

1

180PF

CP4

4

5

CP4

180PF

6

3

180PF

CP4

2

7

180PF

CP4

8

1

MMBD914LT1

CR1

3

1

DRAWN BY:

LAST REVISED:

SHEET:

FOLSOM, CALIFORNIA 95630

1900 PRAIRIE CITY ROAD

87

6

5

4

3

2

1

A

B

C

D

1

2

3

4

5

6

7

8

D

C

B

A

PCG PLATFORM DESIGN

REV:

0.5

PROJECT:

OF 40

TITLE: INTEL(R) 820E CHIPSET 2 DIMM FCPGA REFERENCE BOARD

R

PCG AE

Camino2

DB25_DB9_STK

VCC5

Parallel Port