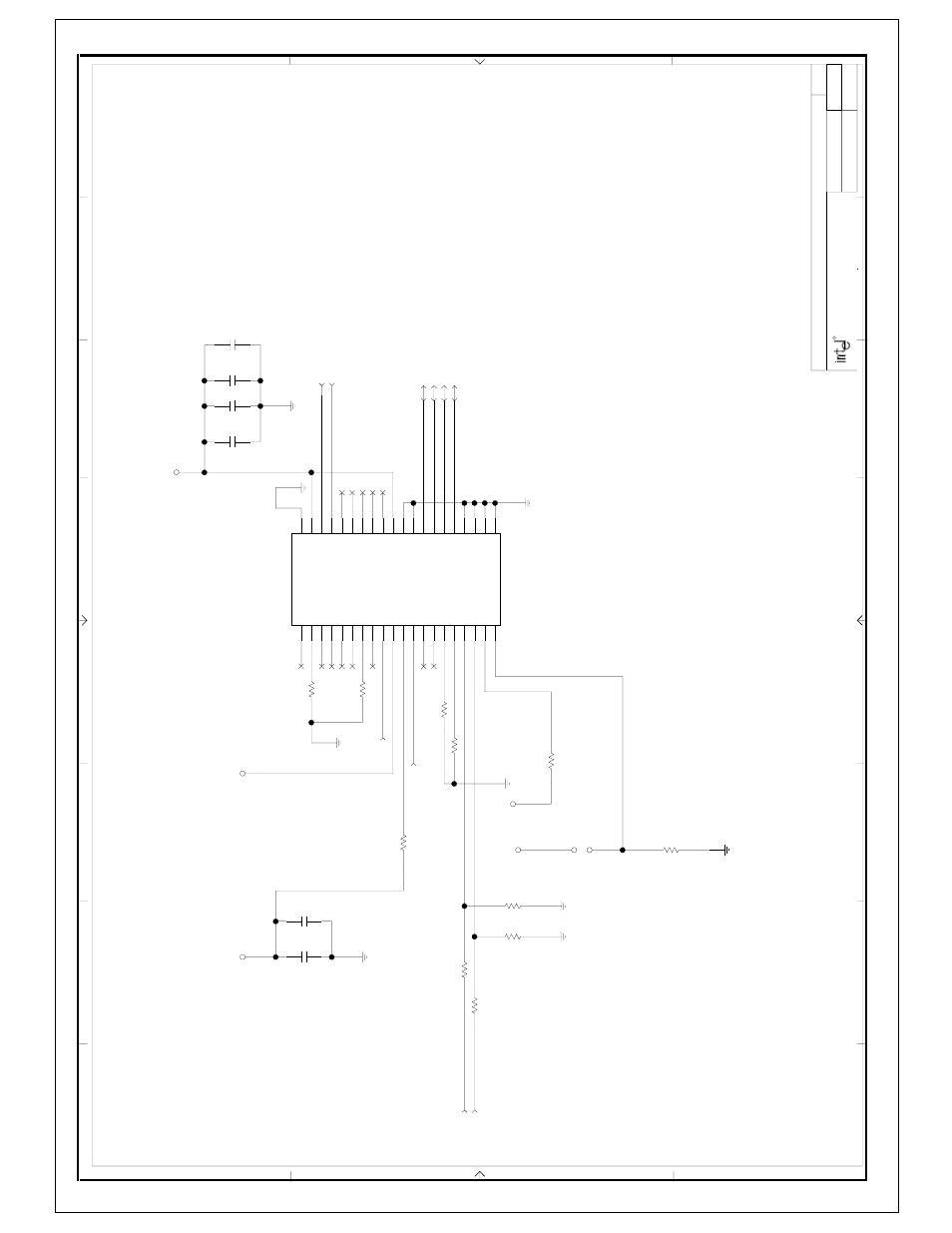

Top block lock – Intel CHIPSET 820E User Manual

Page 206

3-20-2000_10:15

FWH

10

8.2K

R303

FGPI0

FGPI1

R307

10K

R304

10K

TBLK_LCK

9,12

LFRAME#/FWH4

9,12

LAD3/FWH3

LAD2/FWH2

9,12

LAD1/FWH1

9,12

LAD0/FWH0

9,12

6,8,11,12,24,25,26,27

PCIRST#

5

FWHPCLK

WPROT

4,8

HINIT#

R299

0K

JP21

4.7K

R308

8.2K

R298

R296

8.2K

VPP_R

FGPI3

FGPI2

FGPI4

FWH_IC

U16

18

17

16

15

7

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

14

13

12

11

10

9

2

8

6

5

4

3

1

C300

0.1UF

C305

0.1UF

C301

0.1U

F

C298

0.1U

F

0.1U

F

C297

0.1U

F

C308

0K

R306

27

S100DETECT

27

P100DETECT

0K

R305

4.7K

R310

8.2K

R300

DRAWN BY:

LAST REVISED:

SHEET:

FOLSOM, CALIFORNIA 95630

1900 PRAIRIE CITY ROAD

87

6

5

4

3

2

1

A

B

C

D

1

2

3

4

5

6

7

8

D

C

B

A

PCG PLATFORM DESIGN

REV:

0.5

PROJECT:

OF 40

TITLE: INTEL(R) 820E CHIPSET 2 DIMM FCPGA REFERENCE BOARD

R

PCG AE

Camino2

VCC3_3

VCC3_3

VCC3_3

VCC3_3

VCC3_3

NC1

NC3

NC4

NC5

NC6

NC8

IC

CLK

VCC10

VPP

RST#

NC13

NC14

WP#

TBL#

ID3

ID2

ID1

ID0

FWH0

FWH1

FWH2

FWH3

GND29

GND30

VCC31

RFU32

RFU33

RFU34

RFU35

RFU36

INIT#

FWH4

VCCA

GNDA

FGPI4

FGPI3

FGPI2

FGPI1

FGPI0

FWH

Top Block Lock

to VCC3_3 for onboard programming.

Do not tie Vpp to 12V. Vpp should be tied

For host side detection, stuff R304,R305,R306,R307.

For drive side detection, stuff R304,R307. No stuff R305,R306.

FWH