Intel CHIPSET 820E User Manual

Page 218

22

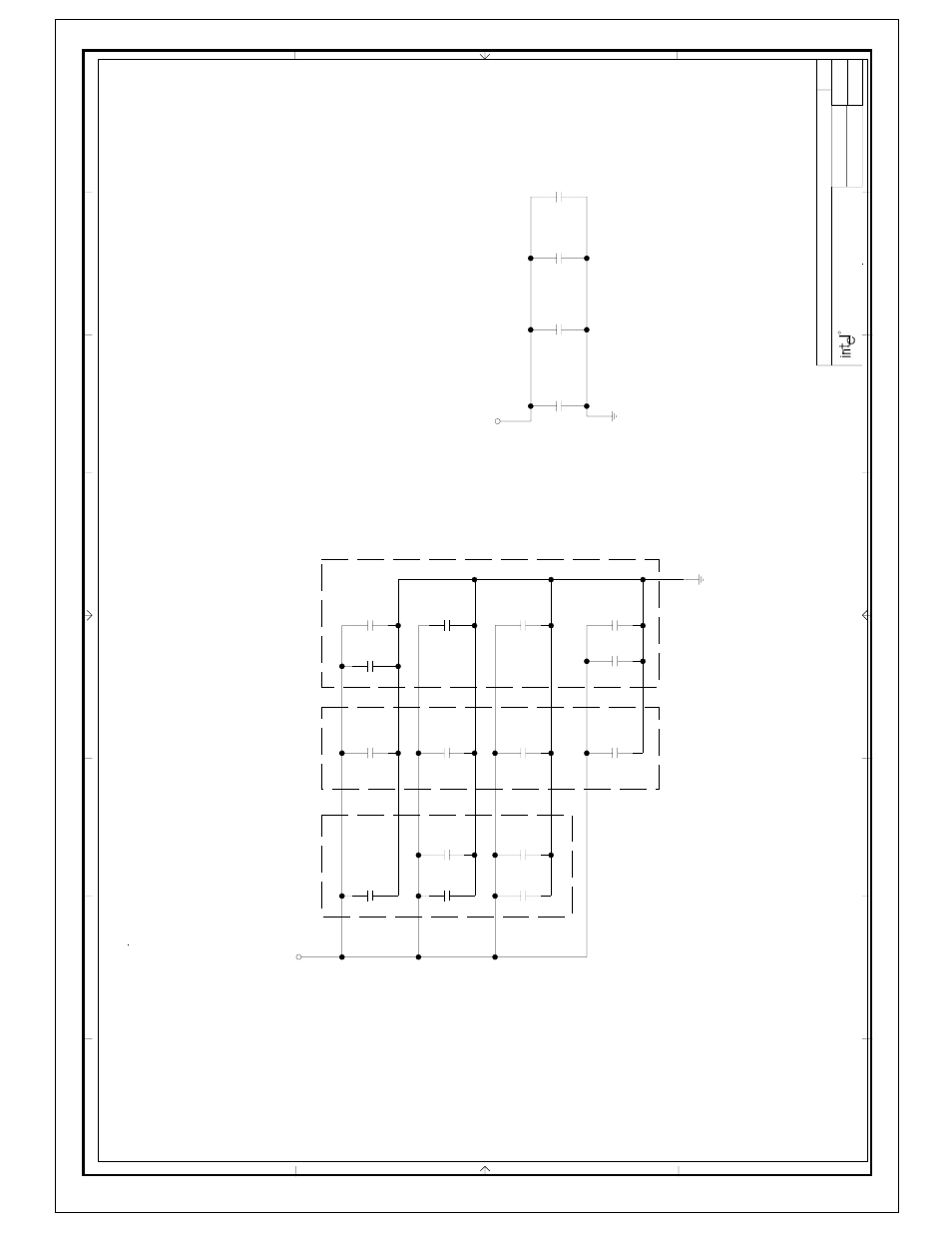

LAN

25V

20%

0.1UF

C387

C388

0.1UF 20% 25V

25V

20%

0.1UF

C389

C390

0.1UF 20% 25V

25V

20%

0.1UF

C384

C385

0.1UF 20% 25V

25V

20%

0.1UF

C380

C381

0.1UF 20% 25V

25V

20%

0.1UF

C382

C383

0.1UF 20% 25V

C378

0.1UF 20% 25V

25V

20%

0.1UF

C377

C375

4.7UF 20% 16V

16V

20%

4.7UF

C370

16V

20%

4.7UF

C366

C376

0.1UF 20% 25V

25V

20%

0.1UF

C379

C369

4.7UF 20% 16V

25V

20%

0.1UF

C386

VCC3_3SBY

DRAWN BY:

LAST REVISED:

SHEET:

FOLSOM, CALIFORNIA 95630

1900 PRAIRIE CITY ROAD

8

765

43

21

A

B

C

D

1

2

3

4

5

6

7

8

D

C

B

A

PCG PLATFORM DESIGN

REV:

0.5

PROJECT:

OF 40

TITLE: INTEL(R) 820E CHIPSET 2 DIMM FCPGA REFERENCE BOARD

R

PCG AE

Camino2

VCC3_3SBY

2: Include at least 0.1uf cap per EEPROM

LAN

STUFF FOR

82562E

H

STUFF FOR GILAD ONLY

1: Bulk Caps (4.7uf) should be palced 1 per side around

Kennereth/+ and 0.1uf caps should be placed near PWR/GND

and high speed signals.

NOTES:

STUFF FOR

82562ET/EM

ONLY

AND

82562E

T/

E

M