Maxim Integrated MAXQ622 User Manual

Page 86

MAXQ612/MAXQ622 User’s Guide

Maxim Integrated

5-13

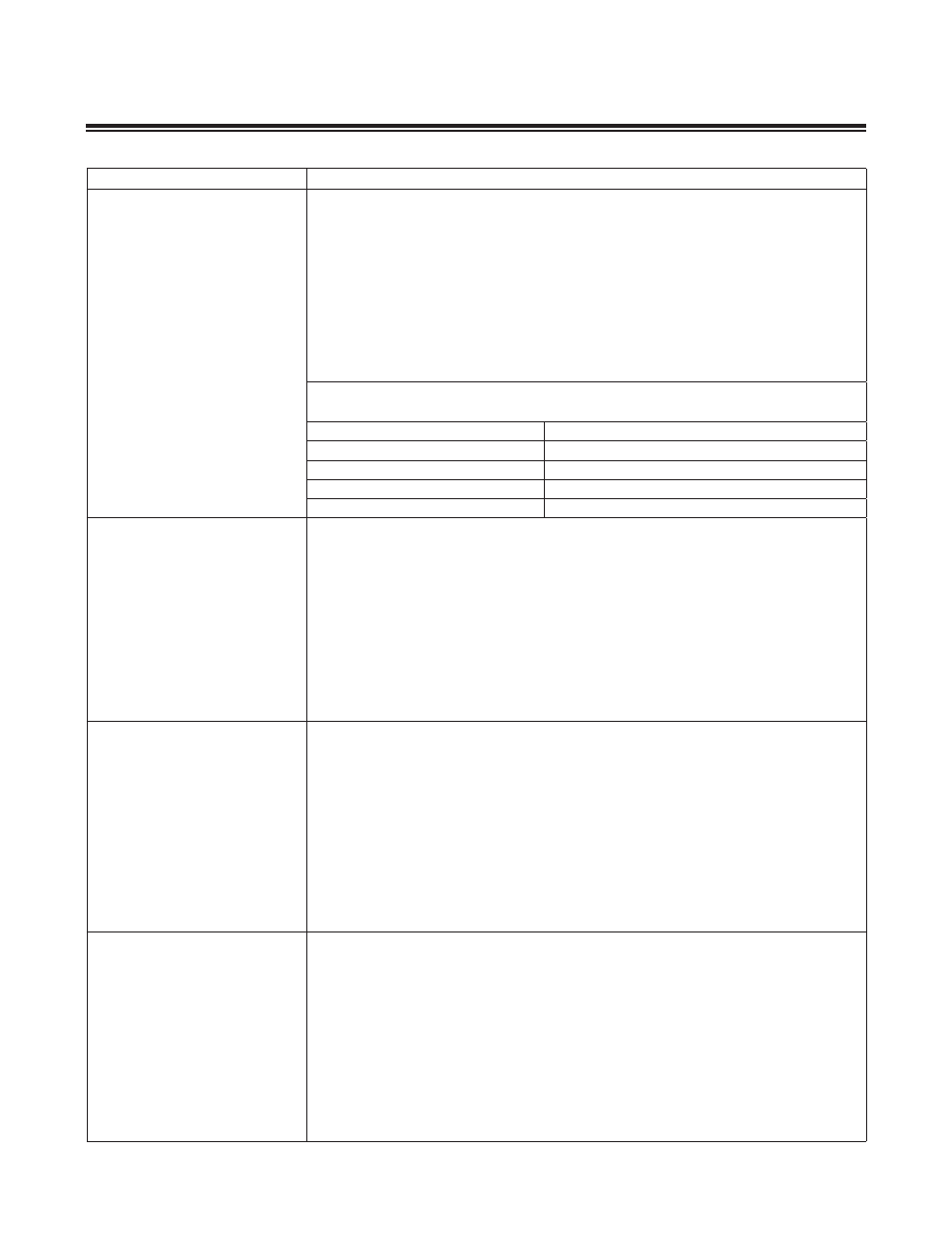

REGISTER

DESCRIPTION

PWCN.12 (CTM)

Crystal Multiplier Enable. The CTM bit is used to enable the crystal clock multiplier .

When programmed to 0, the CTM bit disables the crystal clock multiplier to save energy .

When programmed to 1, the CTM bit enables the crystal clock multiplier . The crystal

clock multiplier requires a startup stabilization period . Clearing the CTM to 0 automatically

clears the CKRY and CTMS bits . Setting CTM to 1 starts the crystal clock multiplier startup

counter . During the startup count, the CKRY bit remains cleared .

PWCN.13 (CKRY)

Clock Ready. The CKRY bit indicates the status of the startup period delay for the USB

clock multiplier PLL warmup period of certain clock cycles . When the CKRY = 0, the counter

for the startup delay is still counting . When the CKRY = 1, the count has been completed .

The CKRY bit is cleared each time the CTMS bit is cleared to 0 and the USB enable is low .

This bit is also cleared by STOP mode .

PWCN.[14:15] (PFWARNCN[1:0])

Power-Fail Warning Trip Point Control [1:0]. These bits are used to change the trip point

voltage for indicating that a power warning has occurred . These two bits are reset only by POR .

PFWARNCN[1:0]

NOMINAL VOLTAGE TRIP POINT (V)

00

1 .8

01

1 .9

10

2 .55

11

2 .75

PD4 (10h, 01h)

Port 4 Direction Register

Initialization:

This register is cleared to 00h on all resets except power-fail reset . This register is

unaffected by power-fail reset .

Read/Write Access:

Unrestricted read/write .

PD4.7 to PD4.0

Port 4 Direction Register Bits 7:0. PD4 is used to determine the direction of the port 4

function . The port pins are independently controlled by their direction bit . When a bit is set

to 1, its corresponding pin is used as an output; data in the PO register is driven on the pin .

When a bit is cleared to 0, its corresponding pin is used as an input, and allows an external

signal to drive the pin . Note that each port pin has a weak pullup circuit when functioning

as an input and the p-channel pullup transistor is controlled by its respective PO bits . If the

PO bit is set to 1, the weak pullup is on, if the PO bit is cleared to 0, the weak pullup is off

and forces the port pin into three-state .

PD5 (11h, 01h)

Port 5 Direction Register

Initialization:

This register is cleared to 00h on all resets except power-fail reset . This register is

unaffected by power-fail reset .

Read/Write Access:

Unrestricted read/write .

PD5.7 to PD5.0

Port 5 Direction Register Bits 7:0. PD5 is used to determine the direction of the port 5

function . The port pins are independently controlled by their direction bit . When a bit is set

to 1, its corresponding pin is used as an output; data in the PO register is driven on the pin .

When a bit is cleared to 0, its corresponding pin is used as an input, and allows an external

signal to drive the pin . Note that each port pin has a weak pullup circuit when functioning

as an input and the p-channel pullup transistor is controlled by its respective PO bits . If the

PO bit is set to 1, the weak pullup is on, if the PO bit is cleared to 0, the weak pullup is off

and forces the port pin into three-state .

PD6 (12h, 01h)

Port 6 Direction Register

Initialization:

This register is cleared to 00h on all resets except power-fail reset . This register is

unaffected by power-fail reset .

Read/Write Access:

Unrestricted read/write .

PD6.7 to PD6.0

Port 6 Direction Register Bits 7:0. PD65 is used to determine the direction of the port 6

function . The port pins are independently controlled by their direction bit . When a bit is set

to 1, its corresponding pin is used as an output; data in the PO register is driven on the pin .

When a bit is cleared to 0, its corresponding pin is used as an input, and allows an external

signal to drive the pin . Note that each port pin has a weak pullup circuit when functioning

as an input and the p-channel pullup transistor is controlled by its respective PO bits . If the

PO bit is set to 1, the weak pullup is on, if the PO bit is cleared to 0, the weak pullup is off

and forces the port pin into three-state .