2 i2c status register (i2cst), 11 .4 .2 i, C status register (i2cst) -9 – Maxim Integrated MAXQ622 User Manual

Page 164: C status register (i2cst)

MAXQ612/MAXQ622 User’s Guide

Maxim Integrated

11-9

Bit 5: I

2

C Data Acknowledge Bit (I2CACK). This bit selects the acknowledge bit returned by the I

2

C controller while

acting as a receiver . Setting this bit to 1 generates a NACK (leaving SDA high) . Clearing the I2CACK bit to 0 generates

an ACK (pulling SDA low) during the acknowledgement cycle . This bit retains its value unless changed by software or

hardware . When an I

2

C abort is in progress (I2CRST = 1), this bit is set to 1 by hardware, and software writes to this

bit are ignored when I2CRST = 1 .

Bit 4: I

2

C Clock Stretch Select (I2CSTRS). Setting this bit to 1 enables clock stretching after the falling edge of the

8th clock cycle . Clearing this bit to 0 enables clock stretching after the falling edge of the 9th clock cycle . This bit has

no effect when clock stretching is disabled (I2CSTREN = 0) .

Bit 2: I

2

C Transfer Mode (I2CMODE). The transfer mode bit selects the direction of data transfer with respect to the

master . When the I2CMODE bit is set to 1, the master is operating in receiver mode (reading from slave) . When the

I2CMODE bit is cleared to 0, the master is operating in transmitter mode (writing to slave) .

Note that software writing to this bit is prohibited in slave mode . When operating in master mode, software configures

this bit to the desired direction of data transfer . When operating in slave mode, the direction of data transfer is deter-

mined by the R//W bit received during the address stage, and this bit reflects the actual R/W bit value in the current

transfer and is set by hardware . Software writing to this bit in slave mode is ignored .

Bit 1: I

2

C Master Mode Enable (I2CMST). The I2CMST bit functions as a master mode enable bit for the I

2

C mod-

ule . When the I2CMST bit is set to 1, the I

2

C operates as a master . When the I2CMST is cleared to 0, the I

2

C module

operates in slave mode . This bit is automatically cleared whenever the I

2

C controller receives a slave address match

(I2CAMI = 1), losses arbitration (I2CALI = 1), or through a general call (I2CGCI = 1) .

Bit 0: I

2

C Enable (I2CEN). This bit enables the I

2

C function . When set to 1, the I

2

C communication unit is enabled .

When cleared to 0, the I

2

C function is disabled .

11.4.2 I

2

C Status Register (I2CST)

Bit 15: I

2

C Bus Busy (I2CBUS). This bit is set to 1 when a START/repeated START condition is detected and cleared

to 0 when the STOP condition is detected . This bit is reset to 0 on all forms of reset and when I2CEN = 0 . This bit is

controlled by hardware and is read only .

Bit 14: I

2

C Busy (I2CBUSY). This bit is used to indicate the current status of the I

2

C module . The I2CBUSY is set to 1

when the I

2

C controller is actively participating in a transaction or when it does not have control of the bus . This bit is

controlled by hardware and is read only .

Bits 13 and 12: Reserved. Reads return 0.

Bit 11: I

2

C STOP Interrupt Flag (I2CSPI). This bit is set to 1 when a STOP condition (P) is detected . This bit must be

cleared to 0 by software once set . Setting this bit to 1 by software causes an interrupt if enabled .

Bit 10: I

2

C SCL Status (I2CSCL). This bit reflects the logic state of SCL signal . This bit is set to 1 when SCL is at a

logic-high (1) and cleared to 0 when SCL is at a logic-low (0) . This bit is controlled by hardware and is read only .

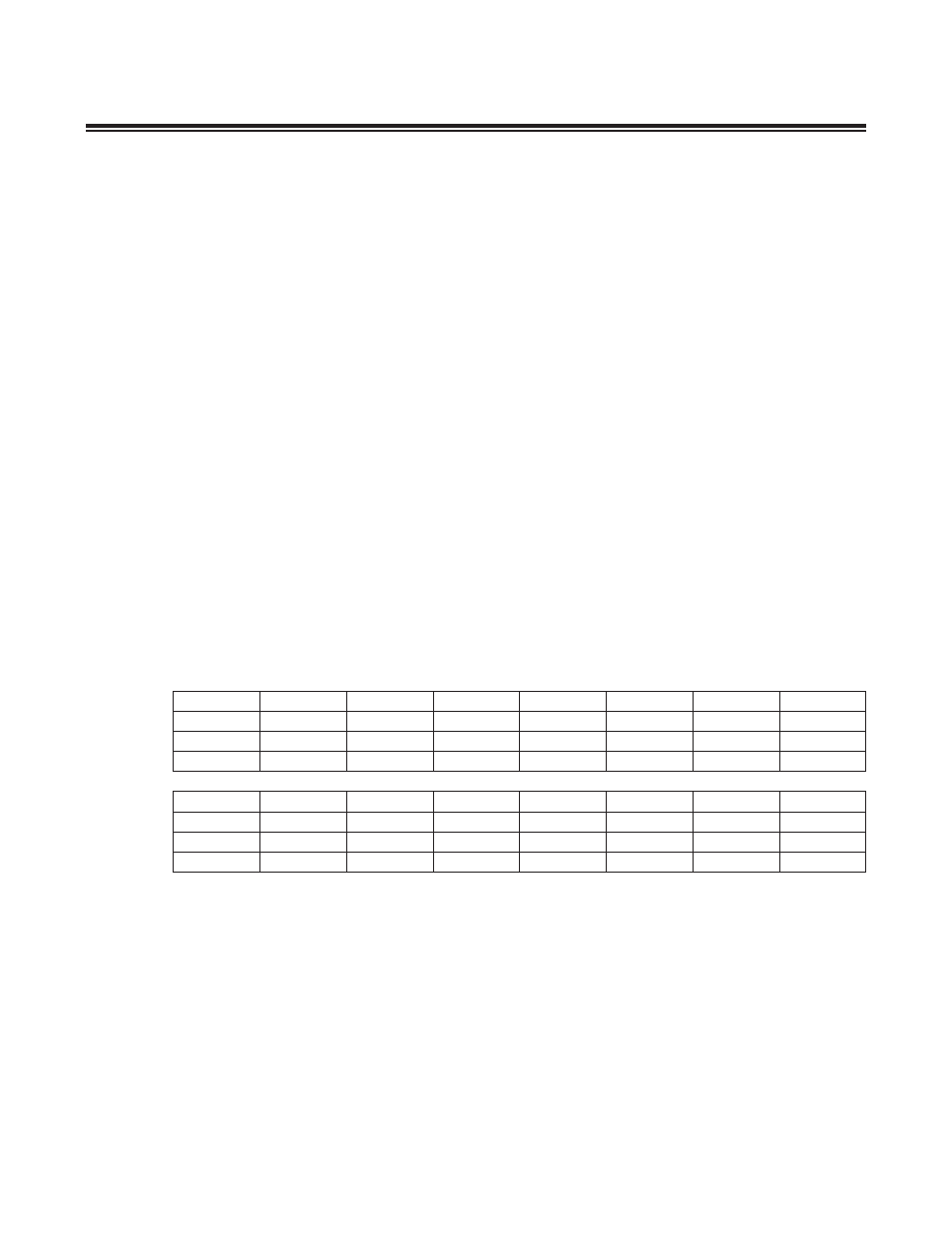

Register Name

I2CST

Register Description

I

2

C Status Register

Register Address

M4[01h]

Bit #

15

14

13

12

11

10

9

8

Name

I2CBUS

I2CBUSY

—

—

I2CSPI

I2CSCL

I2CROI

I2CGCI

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r

rw

r

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

I2CNACKI

I2CALI

I2CAMI

I2CTOI

I2CSTRI

I2CRXI

I2CTXI

I2CSRI

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw