2 usb control register (usbcn), 3 usb configuration register (usbcfg) – Maxim Integrated MAXQ622 User Manual

Page 176

MAXQ612/MAXQ622 User’s Guide

12-6

Maxim Integrated

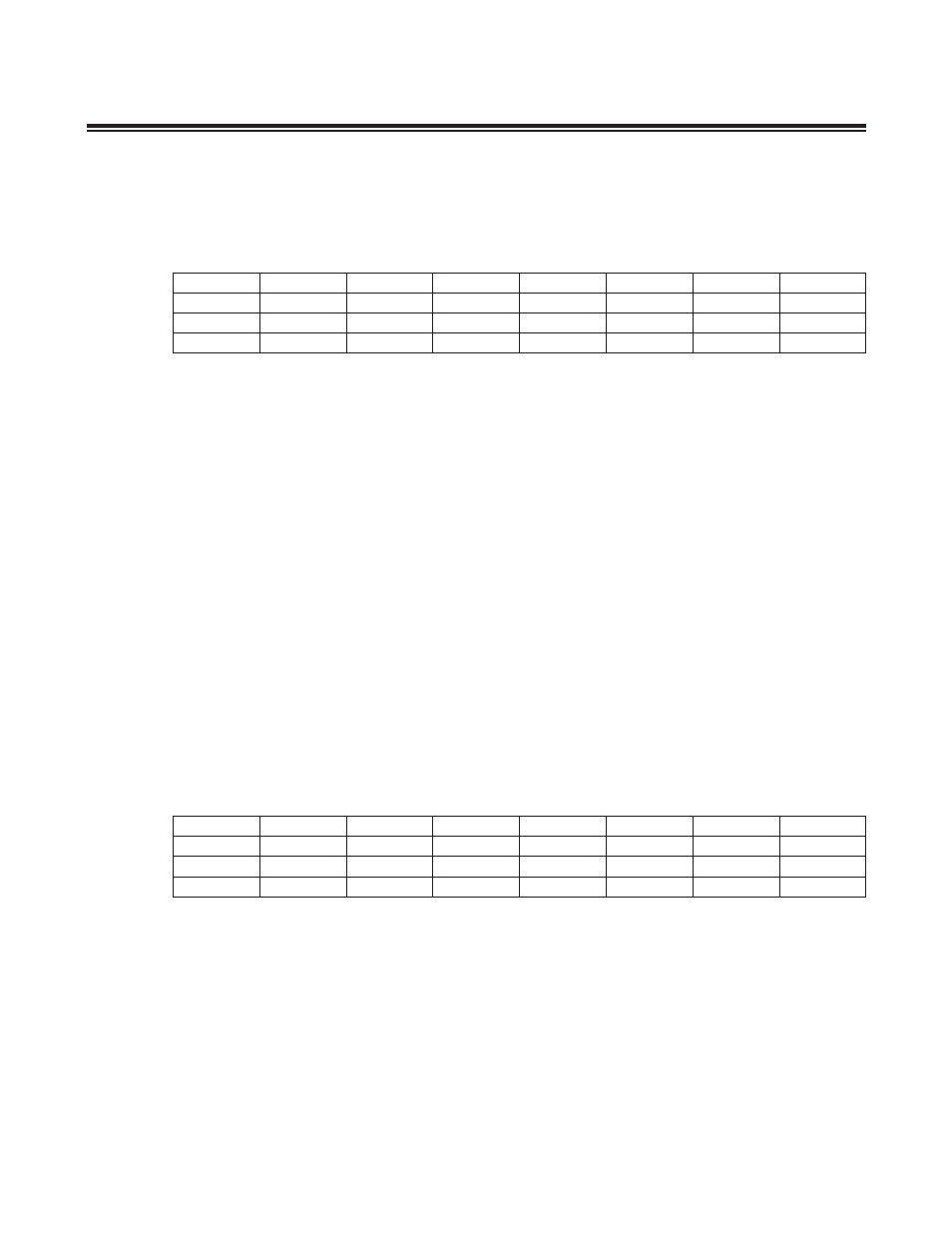

12.4.2 USB Control Register (USBCN)

Bit 7: Oscillator Start (OSCST). Setting this bit to 1 allows the USB controller to enable the oscillator when USB bus

activity is detected on D+ (host resume signaling) . Clearing this bit to 0 keeps the USB controller in low-power state

(inhibit the oscillator from starting) when the USB host resumes bus signaling .

Bit 6: VBUS Gate (VBGATE). Setting this bit to 1 makes operation of the CONNECT bit conditional on VBUS being

present on the VBUS pin . Clearing this bit to 0 makes operation of the CONNECT bit independent of VBUS being valid .

Bit 5: USB Controller Reset (URST). Setting this bit to 1 resets all the USB controller internal states and USB regis-

ters (excluding the USBCN register) to their respective default values . This bit remains set unless cleared by software .

Bit 4: USB Power-Down (PWRDN). Setting this bit to 1 instructs the USB controller to enter a low-power state required

by a USB peripheral in the suspended state . Clearing this bit to 0 takes the USB controller out of the low-power state

and resumes operation .

Bit 3: Connect to USB (CONNECT). Setting this bit to 1 requests the external transceiver to connect an internal 1500I

resistor between the D+ line and V

CC

. Clearing this bit to 0 disconnects the external transceiver internal 1500I resistor

between the D+ line and V

CC

. This goes to the ENUM output pin .

Bit 2: Signal USB Remote Wake-Up (SIGRWU). Setting this bit to 1 signals remote wake-up to the host .

Bits 1 and 0: Reserved. Reads returns zero.

12.4.3 USB Configuration Register (USBCFG)

Note: This register is initialized on POR only.

Note: This register is initialized on POR only.

Bits 7 to 1: Reserved. Reads returns zero.

Bit 0: USB Enable (USBEN). Setting this bit to 1 enables the USB controller . Clearing this bit to 0 disables the USB

controller . Once disabled, the device does not respond to any USB traffic, regardless of the setting in the other USB

register . This bit is cleared following a POR and is unaffected by all other resets .

Register Name

USBCN

Register Description

USB Control Register

Register Address

UADDR[4:0] = 02h

Register Name

USBCFG

Register Description

USB Configuration Register

Register Address

UADDR[4:0] = 03h

Bit #

7

6

5

4

3

2

1

0

Name

OSCST

VBGATE

URST

PWRDN

CONNECT

SIGRWU

—

—

Reset

1

0

1

1

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

—

—

—

—

—

—

—

USBEN

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw