Maxim Integrated MAXQ622 User Manual

Page 100

MAXQ612/MAXQ622 User’s Guide

Maxim Integrated

5-27

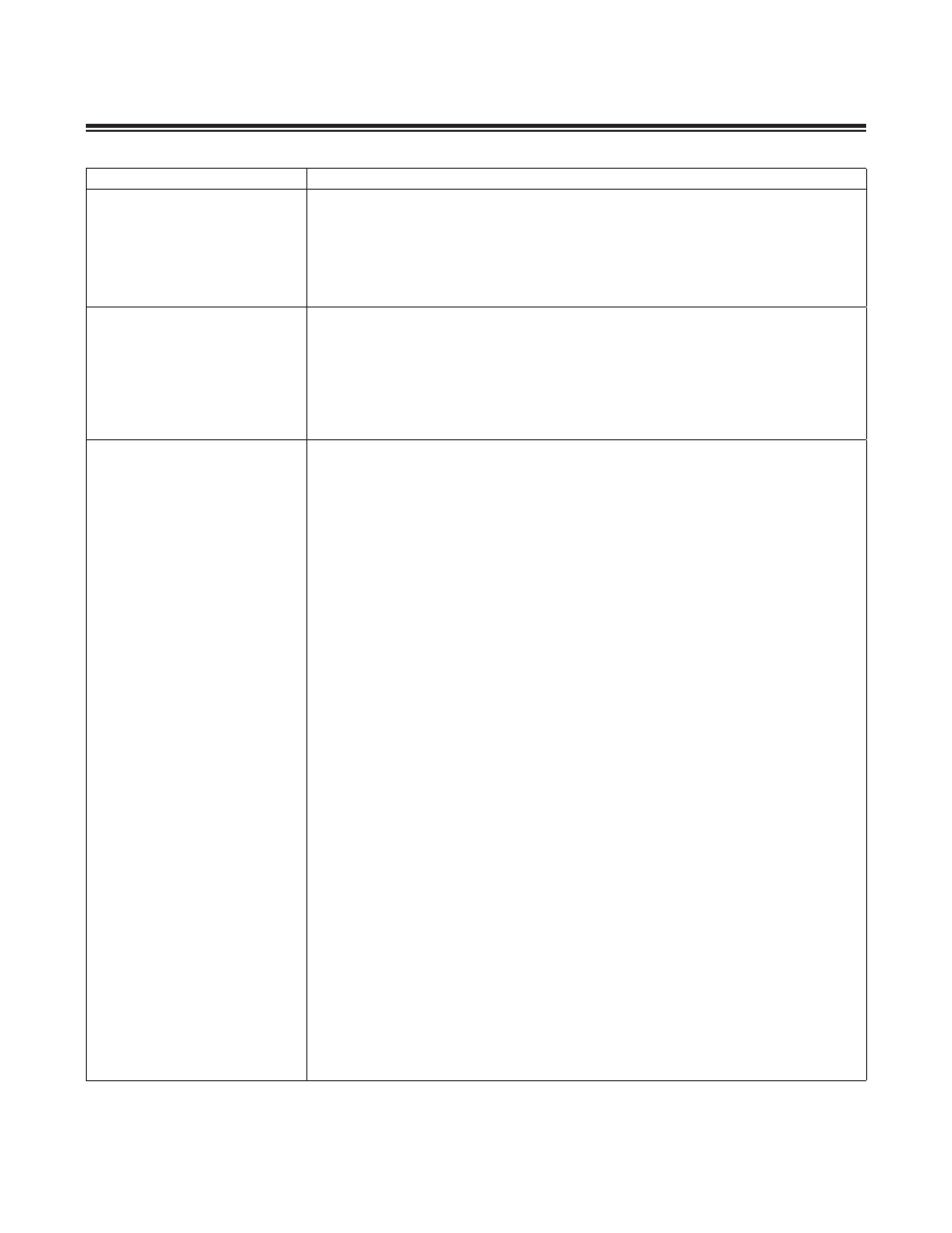

REGISTER

DESCRIPTION

I2CST.14 (I2CBUSY)

I

2

C Busy. This bit is used to indicate the current status of the I

2

C module . The I2CBUSY is

set to 1 when the I

2

C controller is actively participating in a transaction or when it does not

have control of the bus . This bit is controlled by hardware and is read only .

I2CST.15 (I2CBUS)

I

2

C Bus Busy. This bit is set to 1 when a START/repeated START condition is detected and

cleared to 0 when the STOP condition is detected . This bit is reset to 0 on all forms of reset

and when I2CEN = 0 . This bit is controlled by hardware and is read only .

I2CBUF (02h, 04h)

I

2

C Data Buffer Register (8-bit register)

Initialization:

This register is cleared to 00h on all forms of resets

Read/Write Access:

Unrestricted read access . This register can be written to only when I2CBUSY = 0 .

I2CBUF.7 to I2CBUF.0

I

2

C Data Buffer Bits 7:0. Data for I

2

C transfer is read from or written to this location . The

I

2

C transmit and receive buffers are separate, but both are addressed at this location .

During address transmission, only I2CBUF[6:0] is used as the address bits . During data

transmission, only I2CBUF[7:0] is used .

I2CIE (03h, 04h)

I

2

C Interrupt Enable Register (16-bit register)

Initialization:

This register is cleared to 0000h on all forms of reset .

Read/Write Access:

Unrestricted read/write access .

I2CIE.0 (I2CSRIE)

I

2

C START Interrupt Enable. Setting this bit to 1 causes an interrupt to the CPU when a

START condition is detected (I2CSRI = 1) . Clearing this bit to 0 disables a START detection

interrupt from generating .

I2CIE.1 (I2CTXIE)

I

2

C Transmit Complete Interrupt Enable. Setting this bit to 1 causes an interrupt to the

CPU when the transmit interrupt flag is set (I2CTXI = 1) . Clearing this bit to 0 disables the

transmit interrupt from generating .

I2CIE.2 (I2CRXIE)

I

2

C Receive Ready Interrupt Enable. Setting this bit to 1 causes an interrupt to the CPU

when the receive interrupt flag is set (I2CRXI = 1) . Clearing this bit to 0 disables the receive

interrupt from generating .

I2CIE.3 (I2CSTRIE)

I

2

C Clock Stretch Interrupt Enable. Setting this bit to 1 generates an interrupt to the CPU

when the clock stretch interrupt flag is set (I2CSTRI = 1) . Clearing this bit disables the clock

stretch interrupt from generating .

I2CIE.4 (I2CTOIE)

I

2

C Timeout Interrupt Enable. Setting this bit to 1 causes an interrupt to the CPU when

a timeout condition is detected (I2CTOI = 1) . Clearing this bit to 0 disables the timeout

interrupt from generating .

I2CIE.5 (I2CAMIE)

I

2

C Slave Address Match Interrupt Enable. Setting this bit to 1 causes an interrupt to the

CPU when the I

2

C controller detects an address that matches the I2CSLA value (I2CAMI =

1) . Clearing this bit to 0 disables the address match interrupt from generating .

I2CIE.6 (I2CALIE)

I

2

C Arbitration Loss Enable. Setting this bit to 1 causes an interrupt to the CPU when the

I2C master loses in an arbitration (I2CALI = 1) . Clearing this bit to 0 disables the arbitration

loss interrupt from generating .

I2CIE.7 (I2CNACKIE)

I

2

C NACK Interrupt Enable. Setting this bit to 1 causes an interrupt to the CPU when

a NACK is detected (I2CNACKI = 1) . Clearing this bit to 0 disables the NACK detection

interrupt from generating .

I2CIE.8 (I2CGCIE)

I

2

C General Call Interrupt Enable. Setting this bit to 1 generates an I2CGCI (general call

interrupt) to the CPU when general call is enabled (I2CGCEN = 1) . Clearing this bit to 0

disables the general call interrupt from generating .

I2CIE.9 (I2CROIE)

I

2

C Receiver Overrun Interrupt Enable. Setting this bit to 1 causes an interrupt to the CPU

when a receiver overrun condition is detected (I2ROI = 1) . Clearing this bit to 0 disables the

receiver overrun detection interrupt from generating .

I2CIE.10

Reserved. Reads return 0.