9 endpoint nak register (epnak), 10 endpoint clear data toggle register (epctg) – Maxim Integrated MAXQ622 User Manual

Page 181

MAXQ612/MAXQ622 User’s Guide

Maxim Integrated

12-11

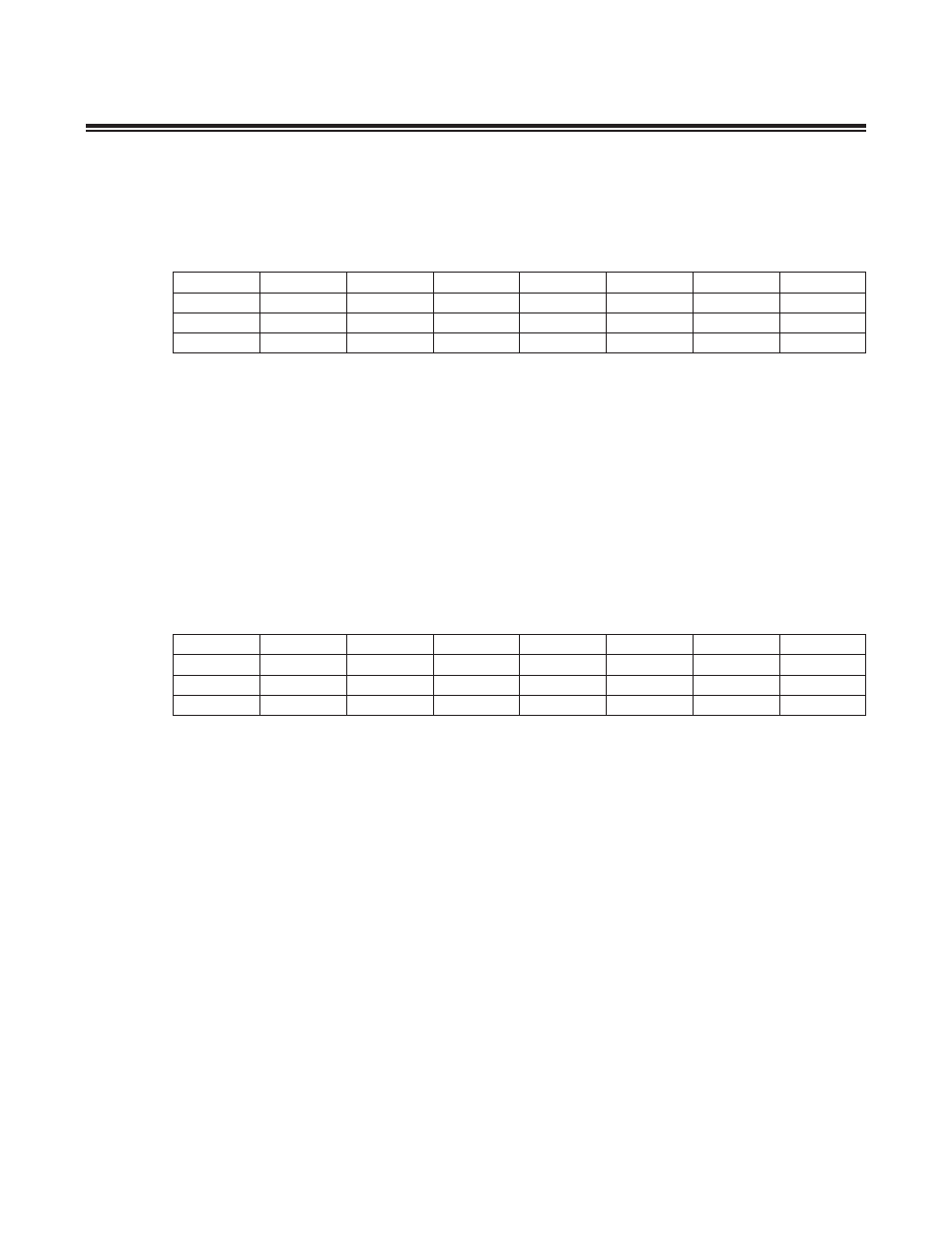

12.4.9 Endpoint NAK Register (EPNAK)

Bit 7: EP3-IN NAK (EP3NAK). The SIE sets this bit when the EP3-IN endpoint receives an IN request and returns the

NAK handshake . This bit remains set unless cleared by software .

Bit 6: EP2-IN NAK (EP2NAK). The SIE sets this bit when the EP2-IN endpoint receives an IN request and returns the

NAK handshake . This bit remains set unless cleared by software .

Bit 5: EP0-IN NAK (EP0NAK). The SIE sets this bit when the EP0-IN endpoint receives an IN request and returns the

NAK handshake . This bit remains set unless cleared by software .

Bits 4 to 0: Reserved. Reads returns zero.

12.4.10 Endpoint Clear Data Toggle Register (EPCTG)

Bit 7: EP3-IN Disable (EP3DIS). Setting this bit to 1 disables traffic to EP3-IN . Clearing this bit to 0 enables traffic to

EP3-IN .

Bit 6: EP2-IN Disable (EP2DIS). Setting this bit to 1 disables traffic to EP2-IN . Clearing this bit to 0 enables traffic to

EP2-IN .

Bit 5: EP1-OUT Disable (EP1DIS). Setting this bit to 1 disables traffic to EP1-OUT . Clearing this bit to 0 enable traffic

to EP1-OUT . Note: Endpoint 0 has no disable bit because as the default control endpoint it must always respond to

a transfer .

Bit 4: Clear EP3-IN Data Toggle (CTGEP3). Setting this bit to 1 clears the data toggle for EP3-IN to the DATA0 state .

This bit is self-cleared by hardware . A USB bus reset also clears this bit to 0 .

Bit 3: Clear EP2-IN Data Toggle (CTGEP2). Setting this bit to 1 clears the data toggle for EP2-IN to the DATA0 state .

This bit is self-cleared by hardware . A USB bus reset also clears this bit to 0 .

Bit 2: Clear EP1-OUT Data Toggle (CTGEP1). Setting this bit to 1 clears the data toggle for EP1-OUT to the DATA0

state . This bit is self-cleared by hardware . A USB bus reset also clears this bit to 0 . Note: Endpoint 0 does not have a

clear data toggle bit . The USB controller handles the data toggle bit for endpoint 0 internally .

Bits 1 and 0: Reserved. Reads returns zero.

Register Name

EPNAK

Register Description

Endpoint NAK Register

Register Address

UADDR[4:0] = 09h

Register Name

EPCTG

Register Description

Endpoint Clear Data Toggle Register

Register Address

UADDR[4:0] = 0Ah

Bit #

7

6

5

4

3

2

1

0

Name

EP3NAK

EP2NAK

EP0NAK

—

—

—

—

—

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

EP3DIS

EP2DIS

EP1DIS

CTGEP3

CTGEP2

CTGEP1

—

—

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw