Table 5-3 . peripheral register reset values -4 – Maxim Integrated MAXQ622 User Manual

Page 77

MAXQ612/MAXQ622 User’s Guide

5-4

Maxim Integrated

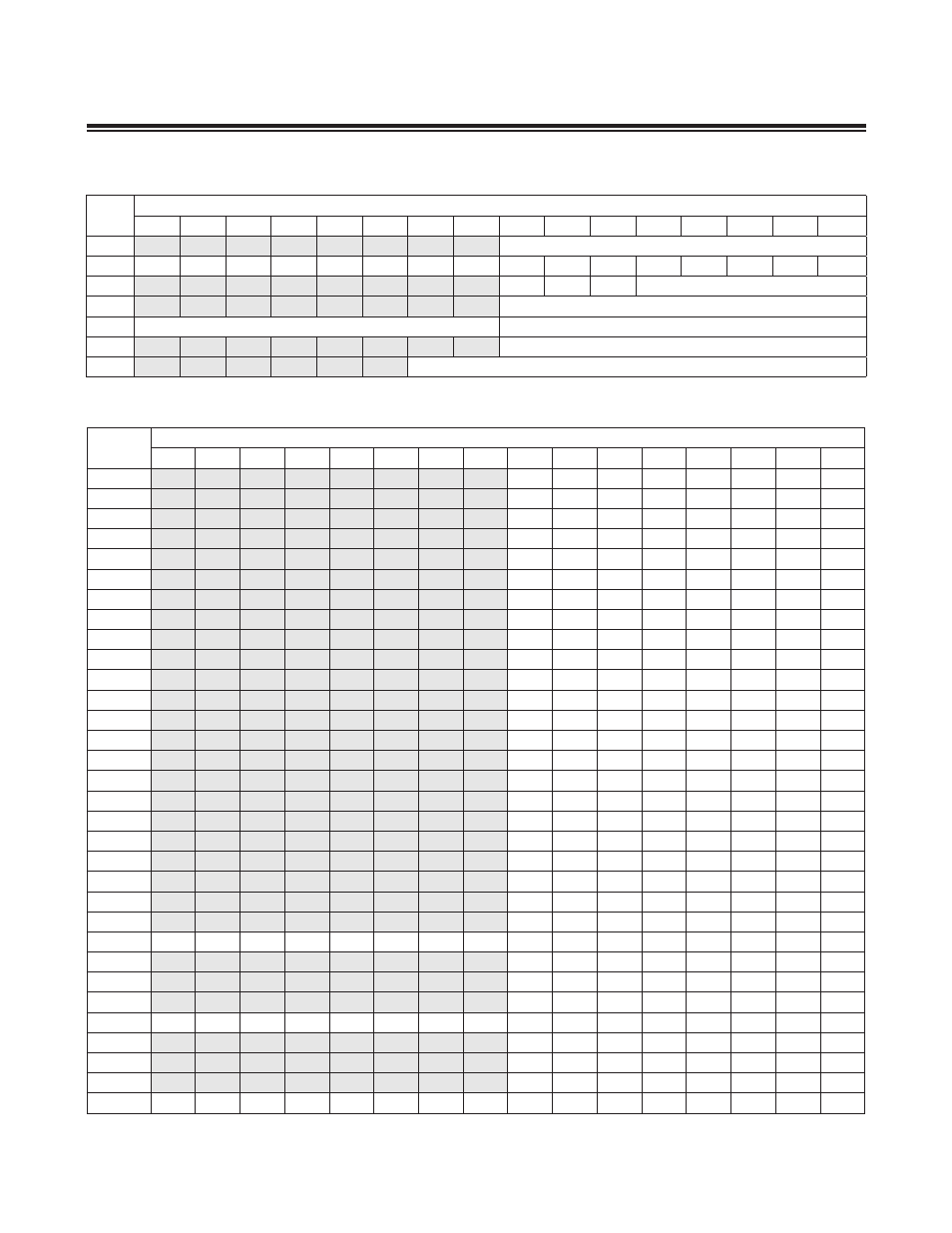

Table 5-3. Peripheral Register Reset Values

Table 5-2. Peripheral Register Bit Function (continued)

REG

BIT

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

PO0

0

0

0

0

0

0

0

0

PO1

0

0

0

0

0

0

0

0

PO2

0

0

0

0

0

0

0

0

PO3

0

0

0

0

0

0

0

0

EIF0

0

0

0

0

0

0

0

0

EIE0

0

0

0

0

0

0

0

0

EIF1

0

0

0

0

0

0

0

0

EIE1

0

0

0

0

0

0

0

0

PI0

s

s

s

s

s

s

s

s

PI1

s

s

s

s

s

s

s

s

PI2

s

s

s

s

s

s

s

s

PI3

s

s

s

s

s

s

s

s

EIES0

0

0

0

0

0

0

0

0

EIES1

0

0

0

0

0

0

0

0

PD0

s

s

s

s

s

s

s

s

PD1

s

s

s

s

s

s

s

s

PD2

s

s

s

s

s

s

s

s

PD3

s

s

s

s

s

s

s

s

CHPREV

s

s

s

s

s

s

s

s

PO4

0

0

0

0

0

0

0

0

PO5

0

0

0

0

0

0

0

0

PO6

0

0

0

0

0

0

0

0

WUTC

0

0

0

0

0

0

0

0

WUT

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

PI4

s

s

s

s

s

s

s

s

PI5

s

s

s

s

s

s

s

s

PI6

s

s

s

s

s

s

s

s

PWCN

0

0

0

0

0

0

s

s

s

1

1

0

0

0

0

0

PD4

s

s

s

s

s

s

s

s

PD5

s

s

s

s

s

s

s

s

PD6

s

s

s

s

s

s

s

s

TB0R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

REG

BIT

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

I2CBUF

I2CBUF[7:0]

I2CIE

—

—

—

—

I2CSPIE

—

I2CROIE I2CGCIE I2CNACKIE I2CALIE I2CAMIE I2CTOIE I2CSTRIE I2CRXIE I2CTXIE

I2CSRIE

UADDR

USBRW UBUSY

—

UADDR[4:0]

UDATA

UDATA[7:0]

I2CCK

I2CCKH[7:0]

I2CCKL[7:0]

I2CTO

I2CTO[7:0]

I2CSLA

I2CLSA[9:0]