7 endpoint interrupt register (epint), 12 .4 .7 endpoint interrupt register (epint) -9 – Maxim Integrated MAXQ622 User Manual

Page 179

MAXQ612/MAXQ622 User’s Guide

Maxim Integrated

12-9

Bit 0: EP0-IN Buffer Available Interrupt Enable (IN0BAVIE). Setting this bit to 1 causes an interrupt to the CPU when

the EP0-IN buffer is available (IN0BAV = 1) . Clearing this bit to 0 disables the buffer ready interrupt from generating .

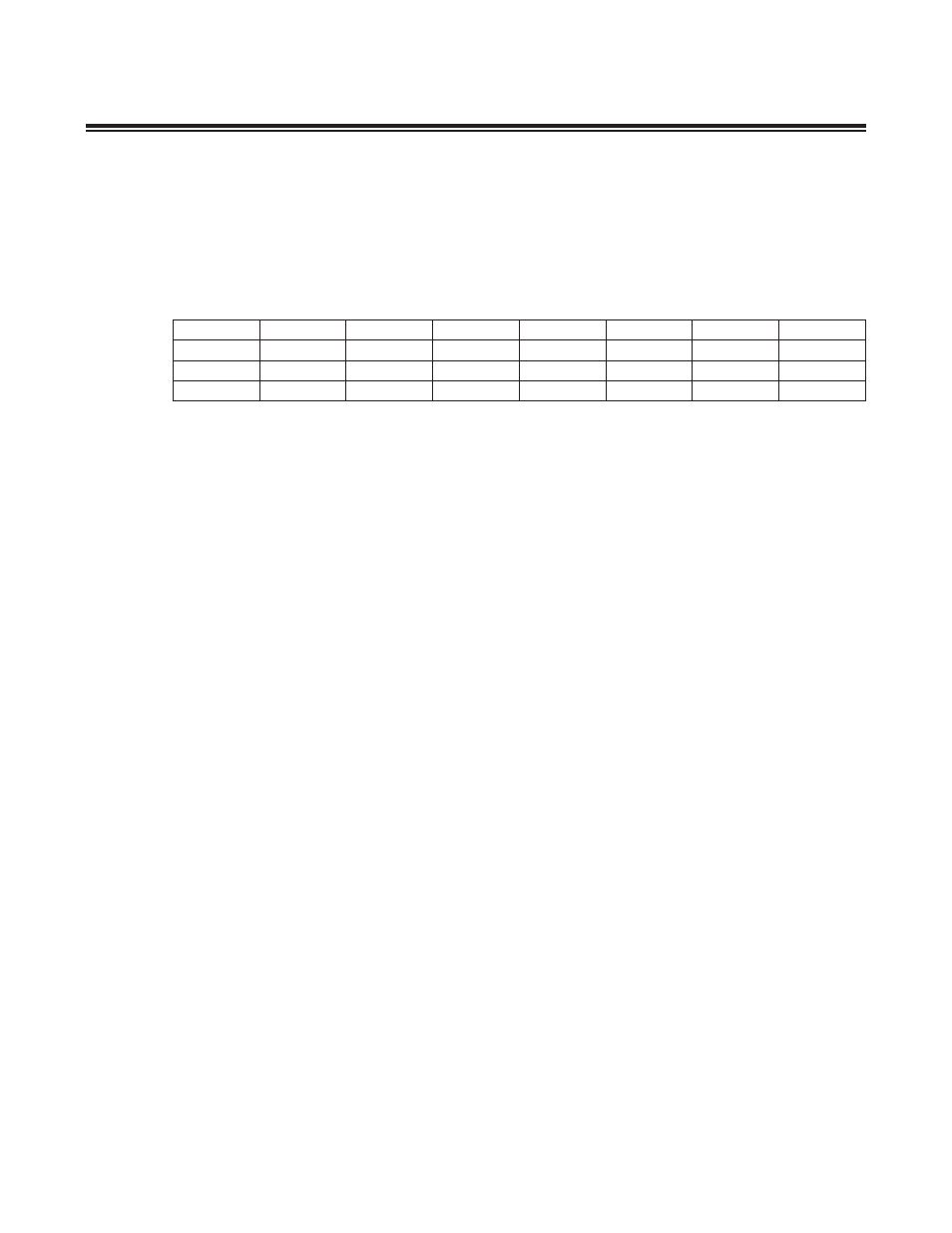

12.4.7 Endpoint Interrupt Register (EPINT)

Bits 7 and 6: Reserved. Reads returns zero.

Bit 5: Setup Data Available (SUDAV). The SIE sets this bit after error-free reception of the eight setup data bytes in a

control transfer . This bit remains set unless cleared by software . Setting SUDAV = 1 generates an interrupt to the CPU

if SUDAVIE is enabled .

Bit 4: EP3-IN Buffer Available (IN3BAV). The SIE sets this bit after receiving an IN token directed to EP3, transfer

data from EP3 buffer and receiving the ACK handshake from the host . This indicates that the EP3 buffer is available

for CPU loading . This bit remains set unless cleared by software or by writing the EP3BC register . Setting IN3BAV = 1

generates an interrupt to the CPU if IN3BAVIE is enabled .

Bit 3: EP2-IN Buffer Available (IN2BAV). The SIE sets this bit after receiving an IN token directed to EP2, transfer

data from EP2 buffer and receiving the ACK handshake from the host . This indicates that the EP2 buffer is available

for CPU loading . This bit remains set unless cleared by software or by writing the EP2BC register . Setting IN2BAV = 1

generates an interrupt to the CPU if IN2BAVIE is enabled .

Bit 2: EP1-OUT Data Available (OUT1DAV). The SIE sets this bit when it has successfully received (and ACK) an OUT

data packet to EP1 buffer . This indicates that the EP1 buffer is available for CPU reading . This bit remains set unless

cleared by software . Clearing this bit also arms the endpoint for another transfer . Setting OUT1BAV = 1 generates an

interrupt to the CPU if OUT1DAVIE is enabled .

Bit 1: EP0-OUT Data Available (OUT0DAV). The SIE sets this bit when it has successfully received (and ACK) an OUT

data packet to EP0 buffer . This indicates that the EP0 buffer is available for CPU reading . This bit remains set unless

cleared by software . Clearing this bit also arms the endpoint for another transfer . Setting OUT0BAV = 1 generates an

interrupt to the CPU if OUT0DAVIE is enabled .

Bit 0: EP0-IN Buffer Available (IN0BAV). The SIE sets this bit after receiving an IN token directed to EP0, transfer

data from EP0 buffer and receiving the ACK handshake from the host . This indicates that the EP0 buffer is available

for CPU loading . This bit remains set unless cleared by software or by writing the EP0BC register . Setting IN0BAV = 1

generates an interrupt to the CPU if IN0BAVIE is enabled .

Register Name

EPINT

Register Description

Endpoint Interrupt Register

Register Address

UADDR[4:0] = 07h

Bit #

7

6

5

4

3

2

1

0

Name

—

—

SUDAV

IN3BAV

IN2BAV

OUT1DAV

OUT0DAV

IN0BAV

Reset

0

0

0

1

1

0

0

1

Access

rw

rw

rw

rw

rw

rw

rw

rw