5 interrupt exception window, 10 operating modes, 11 reset mode – Maxim Integrated MAXQ622 User Manual

Page 33: 1 power-on/power-fail reset, 2 .9 .5 interrupt exception window -29, 2 .10 operating modes -29 2 .11 reset mode -29, 2 .11 .1 power-on/power-fail reset -29, Table 2-9 . power-fail reset check interval -29

MAXQ612/MAXQ622 User’s Guide

Maxim Integrated

2-29

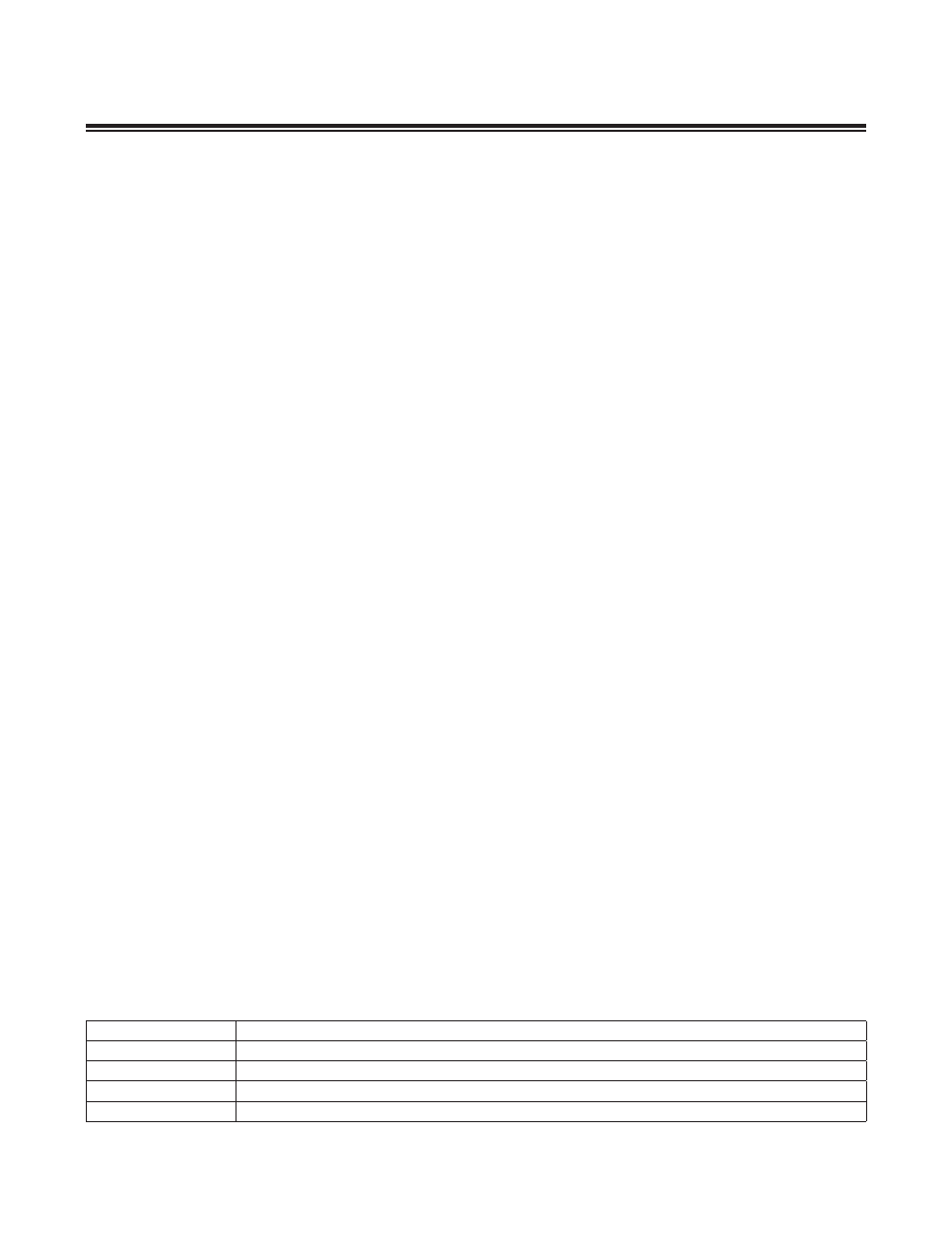

Table 2-9. Power-Fail Reset Check Interval

2.9.5 Interrupt Exception Window

An interrupt exception window is a noninterruptible execution cycle . During this cycle, the interrupt handler does not

respond to any interrupt requests . All interrupts that would normally be serviced during an interrupt exception window

are delayed until the next execution cycle .

Interrupt exception windows are used when two or more instructions must be executed consecutively without any

delays in between . There are two conditions in the MAXQ612/MAXQ622 microcontrollers that cause an interrupt excep-

tion window:

• Activation of the prefix register (PFX[n])

• Code memory access using the code pointer (CP)

When the prefix register (PFX[n]) is activated by writing a value to it, it retains that value only for the next clock cycle .

For the prefix value to be used properly by the next instruction, the instruction that sets the prefix value and the instruc-

tion that uses it must always be executed back to back . Therefore, writing to the PFX[n] register causes an interrupt

exception window on the next cycle .

The one-cycle stall when using the code pointer is due to the fact that the current instruction could also be accessing

the stack .

If an interrupt occurs during an interrupt exception window, an additional latency of one cycle in the interrupt handling

is caused as the interrupt is not serviced until the next cycle .

2.10 Operating Modes

In addition to the standard program execution mode, the MAXQ612/MAXQ622 can also be in three other operating

modes . During reset mode, the processor is temporarily halted by an external or internal reset source . During power-

management mode, the processor executes instructions at a reduced clock rate in order to decrease power consump-

tion . Finally, stop mode halts execution and all internal clocks (with the exception of the wake-up timer if enabled) to

save power until an external stimulus indicates that processing should be resumed .

2.11 Reset Mode

When the MAXQ612/MAXQ622 microcontrollers are in reset mode, no instruction execution or other system or peripher-

al operations occur, and all input/output pins return to default states . Once the condition that caused the reset (whether

internal or external) is removed, the processor begins executing code from utility ROM at address 8000h .

There are four different sources that can cause the MAXQ612/MAXQ622 to enter reset mode:

• Power-on/power-fail reset

• External reset

• Watchdog timer reset

• Internal system reset

2.11.1 Power-On/Power-Fail Reset

An on-chip power-on reset (POR) circuit is provided to ensure proper initialization on internal device states . The POR

circuit provides a minimum POR delay sufficient to accomplish this initialization . For fast V

DD

supply rise times, the

MAXQ612/MAXQ622 are, at a minimum, held in reset for the POR delay when initially powered up . For slow V

DD

supply

rise times, the MAXQ612/MAXQ622 are held in reset until V

DD

is above the POR voltage threshold .

PFRCK[1:0]

POWER-FAIL MONITOR CHECK INTERVAL (NANOPOWER RING OSCILLATOR CYCLES)

00

No interval defined (Monitor on always as normal)

01

2

10

(~ 128ms for 8kHz nanopower ring oscillator frequency)

10

2

11

(~ 256ms for 8kHz nanopower ring oscillator frequency)

11

2

12

(~ 512ms for 8kHz nanopower ring oscillator frequency)