8 interrupt function – Epson S1C88650 User Manual

Page 81

S1C88650 TECHNICAL MANUAL

EPSON

73

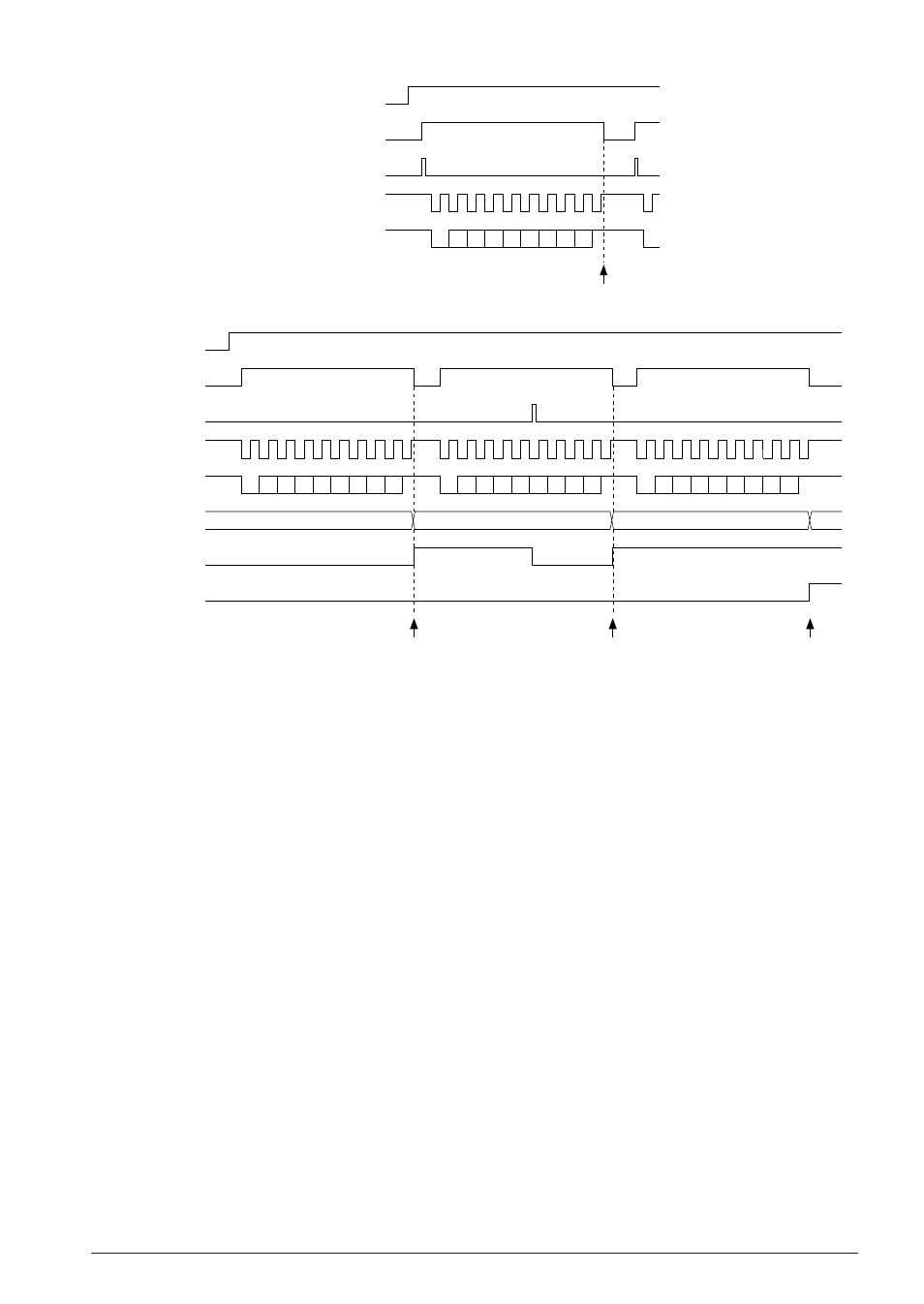

5 PERIPHERAL CIRCUITS AND THEIR OPERATION (Serial Interface)

TXEN

TXTRG(RD)

TXTRG(WR)

SOUT

Interrupt

(In 8-bit mode/Non parity)

D0 D1 D2 D3 D4 D5 D6 D7

Sumpling

clock

(a) Transmit timing

RXEN

RXTRG(RD)

RXTRG(WR)

SIN

TRXD

OER control signal

OER

Interrupt

(In 8-bit mode/Non parity)

D0 D1 D2 D3 D4 D5 D6 D7

D0 D1

D6 D7

D0 D1 D2 D3 D4 D5 D6 D7

D2 D3 D4 D5

1st data

2st data

Sumpling

clock

(b) Receive timing

Fig. 5.8.7.4 Timing chart (asynchronous transfer, LSB first, stop bit = 1 bit)

5.8.8 Interrupt function

This serial interface includes a function that

generates the below indicated three types of

interrupts.

• Transmitting complete interrupt

• Receiving complete interrupt

• Error interrupt

The interrupt factor flag FSxxx and the interrupt

enable register ESxxx for the respective interrupt

factors are provided and then the interrupt enable/

disable can be selected by the software. In addition,

a priority level of the serial interface interrupt for

the CPU can be optionally set at levels 0 to 3 by the

interrupt priority registers PSIF0 and PSIF1.

For details on the above mentioned interrupt

control register and the operation following

generation of an interrupt, see "5.14 Interrupt and

Standby Status".

Figure 5.8.8.1 shows the configuration of the serial

interface interrupt circuit.

■

Transmitting complete interrupt

This interrupt factor is generated at the point where

the sending of the data written into the shift

register has been completed and sets the interrupt

factor flag FSTRA to "1". When set in this manner, if

the corresponding interrupt enable register ESTRA

is set to "1" and the corresponding interrupt priority

registers PSIF0 and PSIF1 are set to a higher level

than the setting of interrupt flags (I0 and I1), an

interrupt will be generated to the CPU.

When "0" has been written into the interrupt enable

register ESTRA and interrupt has been disabled, an

interrupt is not generated to the CPU. Even in this

case, the interrupt factor flag FSTRA is set to "1".

The interrupt factor flag FSTRA is reset to "0" by

writing "1".

The following transmitting data can be set and the

transmitting start (writing "1" to TXTRG) can be

controlled by generation of this interrupt factor.

The exception processing vector address is set as

follows:

Transmitting complete interrupt: 00002CH