3 watchdog timer, 1 configuration of watchdog timer, 2 interrupt function – Epson S1C88650 User Manual

Page 47

S1C88650 TECHNICAL MANUAL

EPSON

39

5 PERIPHERAL CIRCUITS AND THEIR OPERATION (Watchdog Timer)

5.3 Watchdog Timer

5.3.1 Configuration of watchdog timer

The S1C88650 is equipped with a watchdog timer

driven by OSC1 as source oscillation. The watchdog

timer must be reset periodically by software, and if

reset does not take place within the selected period,

a non-maskable interrupt signal is generated and

output to the CPU. The watchdog timer starts

operating after initial reset, however, it can be

stopped by the software.

_______

The NMI generation cycle by the watchdog timer

can be selected by mask option.

_____

Watchdog timer NMI generation cycle

■

■

32768/f

OSC1

(0.75–1-sec cycle when f

OSC1

= 32 kHz)

■

■

65536/f

OSC1

(1.5–2-sec cycle when f

OSC1

= 32 kHz)

■

■

131072/f

OSC1

(3–4-sec cycle when f

OSC1

= 32 kHz)

■

■

262144/f

OSC1

(6–8-sec cycle when f

OSC1

= 32 kHz)

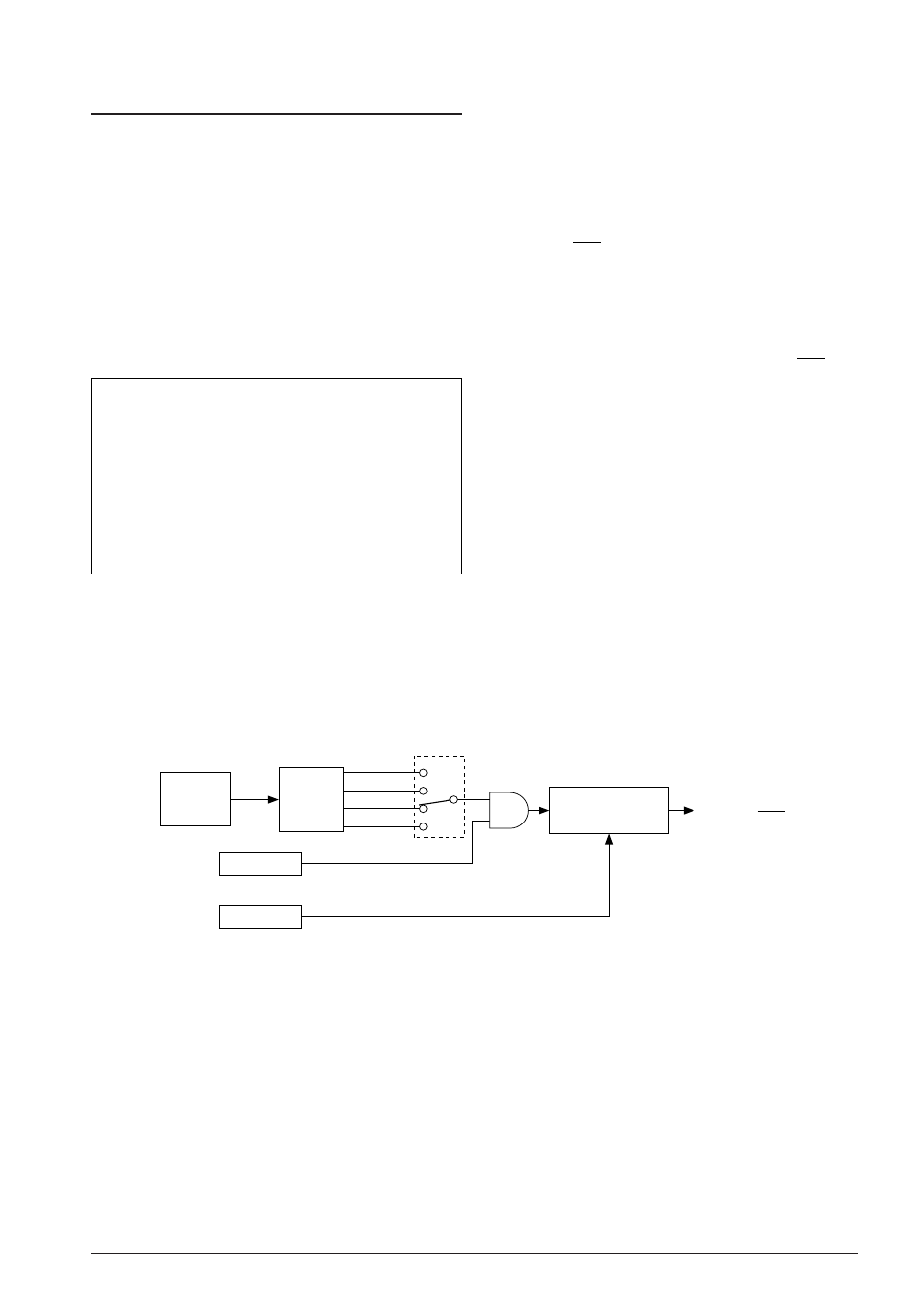

Figure 5.3.1.1 is a block diagram of the watchdog

timer.

By running watchdog timer reset during the main

routine of the program, it is possible to detect

program runaway as if watchdog timer processing

had not been applied.

Normally, this routine is integrated at points that

are regularly being processed.

The watchdog timer continues to operate during

HALT and when HALT state is continuous for

longer than the selected period, the CPU starts

exception processing.

During SLEEP, the watchdog timer is stopped.

Note: The NMI generation cycles in the watchdog

timer mask option list represent maximum

values. A maximum minus (

depending on the watchdog timer reset

timing. For example, when 131072/f

OSC1

is

selected by mask option, the actual NMI

generation cycle is within the range of

98304/f

OSC1

to 131072/f

OSC1

seconds.

5.3.2 Interrupt function

In cases where the watchdog timer is not periodi-

cally reset in software, the watchdog timer outputs

______

an interrupt signal to the CPU's NMI (level 4) input.

Unmaskable and taking priority over other inter-

rupts, this interrupt triggers the generation of

exception processing. See the "S1C88 Core CPU

______

Manual" for more details on NMI exception

processing.

This exception processing vector is set at 000004H.

Watchdog timer

reset signal

Watchdog timer

enable signal

Non-maskable

interrupt (NMI)

Watchdog timer

1/4

WDRST

WDEN

Divider

f

OSC1

OSC1

oscillation

circuit

1/16384

1/32768

1/65536

1/131072

Mask option

Fig. 5.3.1.1 Block diagram of watchdog timer