Simulation, Hardware testing, Performance and resource utilization – Altera Hybrid Memory Cube Controller User Manual

Page 8: Simulation -5, Hardware testing -5, Performance and resource utilization -5

Simulation

Altera performs the following tests on the HMC Controller IP core in simulation, using the Micron HMC

BFM:

• Constrained random tests that cover randomized legal payload sizes and contents

• Assertion based tests to confirm proper behavior of the IP core with respect to the specification

• Extensive coverage of packet retry functionality

Constrained random techniques generate appropriate stimulus for the functional verification of the IP

core. Altera monitors line, expression, and assertion coverage metrics to ensure that all important features

are verified.

Hardware Testing

Altera performs hardware testing of the key functions of the HMC Controller IP core. The Altera

hardware tests of the HMC Controller IP core also ensure reliable solution coverage for hardware related

areas such as performance, link initialization, and reset recovery.

Altera performs hardware testing on the Arria 10 GX FPGA Development Kit with an HMC mezannine

card. A Micron HMC 15G-SR device on the mezzannine card is connected to the development board

through FMC connectors.

Performance and Resource Utilization

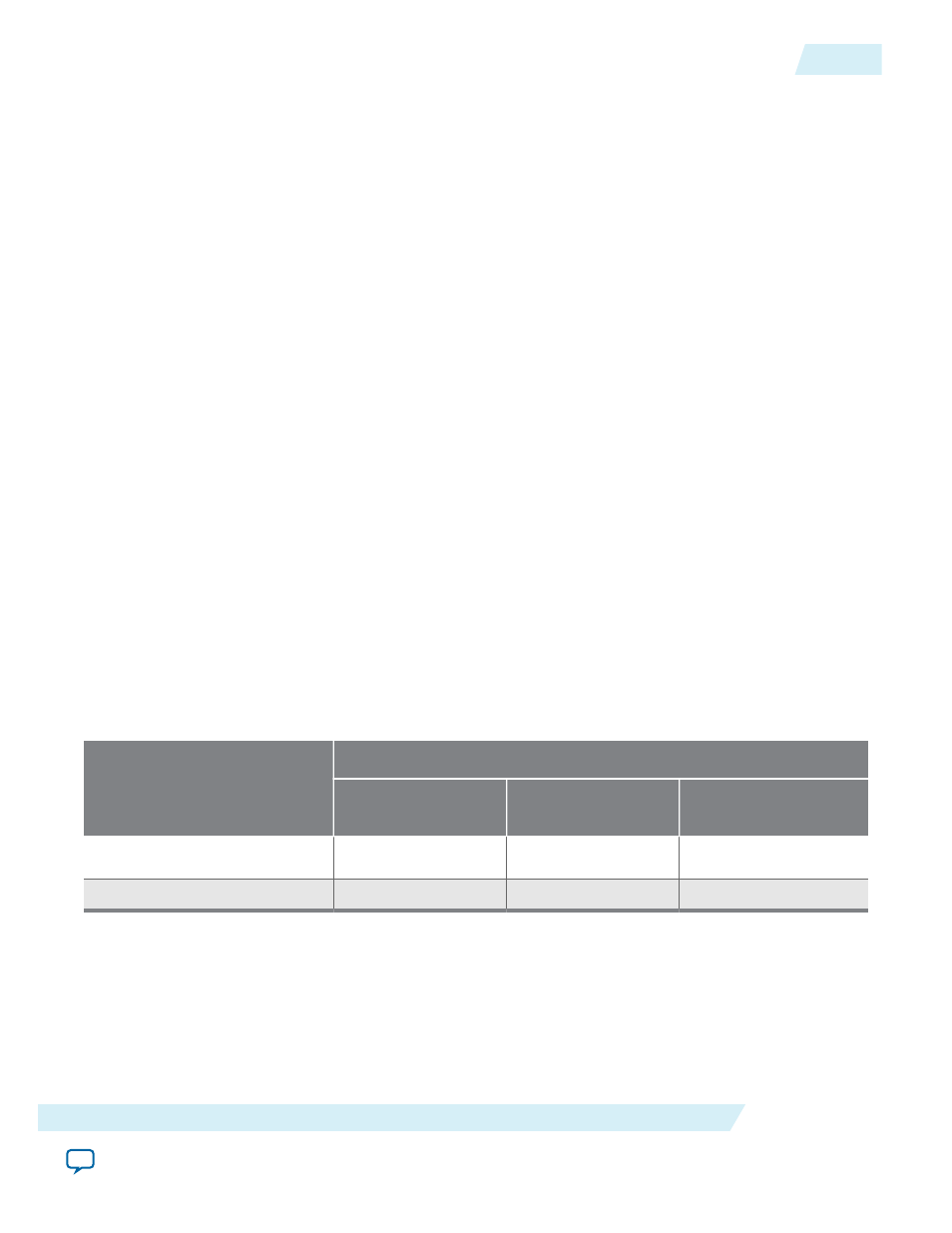

Table 1-3: HMC Controller IP Core FPGA Resource Utilization

Typical resource utilization for an HMC Controller IP core configured with a data rate of 10 Gbps, using the

Quartus II software v15.0, targetting a 10AX115S3F45I2SGE2 device, with IP core features ADME support and

M20K ECC support both turned off.

The numbers of ALMs and logic registers are rounded up to the nearest 100. The numbers of ALMs, before

rounding, are the ALMs needed numbers from the Quartus II Fitter Report.

IP Core Variation

Resource Utilization

ALMs Needed

Dedicated Logic

Registers

M20K Blocks

Half-width

11500

23600

37

Full-width

19700

40900

50

Related Information

•

Information about Quartus II resource utilization reporting, including ALMs needed.

•

UG-01152

2015.05.04

Simulation

1-5

About the Altera Hybrid Memory Cube Controller IP Core

Altera Corporation